信号の分解:デルタ-シグマADCでのアンプ・ノイズの影響:アナログ設計のきほん【ADCとノイズ】(6)(4/5 ページ)

今回と次回は、アンプのノイズがデルタ-シグマA/Dコンバーター(ADC)に与える影響について考察します。まずは、「出力換算ノイズと入力換算ノイズ」「ADCの入力にアンプを追加」「低分解能ADCと高分解能ADCの比較」について扱います。

低分解能ADCと高分解能ADCの比較

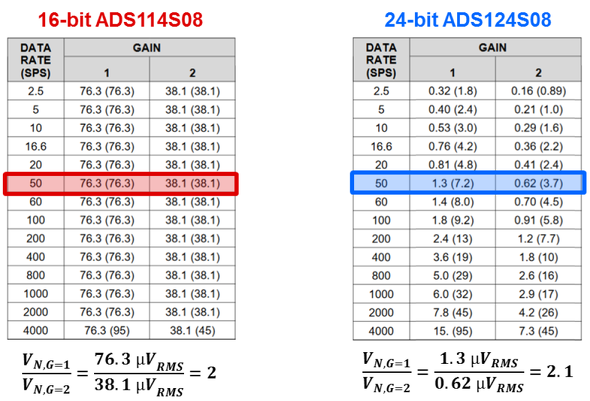

図7に示すのは、『ADS114S08』と『ADS124S08』について、使用できる全てのデータレートに対するゲイン1V/Vおよび2V/Vでの入力換算ノイズです。データレートをどれか選択し(例えば50SPS)、各ゲインでの入力換算ノイズの比をとると、どちらのADCでもほぼ2となります。言い換えれば、ゲインが2倍に増加するとき、同時にノイズは1/2に減少します。この場合、ゲインを追加することで、高分解能(24ビット)と低分解能(16ビット)のADC両方でシステムのノイズ特性が改善します。

図7:G = 1および2V/Vでの入力換算ノイズ(VRMS [VPP])の表 AVDD = 3.3V、AVSS = 0V、PGA有効、グローバルチョッピング無効、内部基準電圧2.5VでのSINC3フィルター(クリックで拡大)

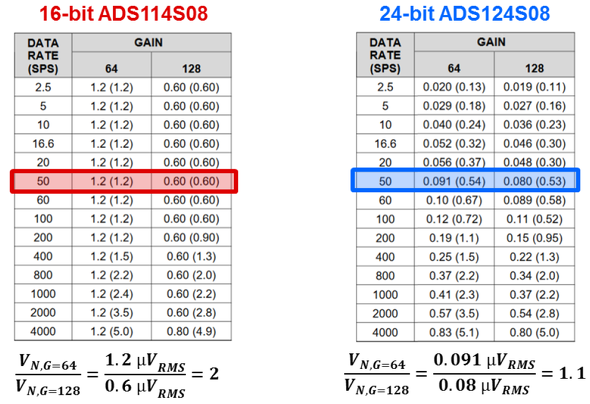

これを図8の場合と比べてください。図8では、64V/Vおよび128V/Vの最高ゲインを使用して同じ計算をしています。低分解能のADCでは比率が2のままですが、高分解能のADCでは約1に減少しています。この高分解能ADCの例では、ゲインが増加してもノイズ特性の向上につながっていません。なぜこの違いが生まれるのでしょうか。

図8:G = 64および128 V/Vでの入力換算ノイズ(VRMS [VPP])の表 AVDD = 3.3V、AVSS = 0V、PGA有効、グローバルチョッピング無効、内部基準電圧2.5VでのSINC3フィルター(クリックで拡大)

分解能が低い(量子化ノイズが支配的な)ADCでゲイン間の比率が一定である理由は、アンプのノイズに比べてADCのノイズのレベルが高いからです。この場合、ADCのノイズがアンプのノイズよりずっと大きいため、式4で記述された条件は満たされません。ADCのノイズは、ゲインを2倍に増加させるたびに確かに減少します。しかし、その最低レベル(G = 128V/V)でも、アンプのノイズと比べて依然としてADCのノイズが支配的です。そのため、実際に測定でアンプノイズが「見える」ことはなく、この特定のシグナルチェーンはアンプの性能にあまり左右されないため、ゲイン値を大きくすることでノイズ特性を改善できる可能性があります。

分解能が高い(熱ノイズが支配的な)ADCの場合は、両方のADCで用いられるアンプが同じだとしても、逆のことが言えます。この場合、ゲインで逓倍されたアンプノイズと比べてADCのノイズがかなり低いため、式4の条件を満たします。結果として、VN,RTIは実質的に一定になり、ゲインを増やしても入力換算ノイズ性能は事実上変化しません。このような状況では、アンプ性能が非常に重要です。多くの場合、アンプを使用すると、まったくアンプを使用しないシステムよりもシステムの分解能が悪くなります。

Copyright © ITmedia, Inc. All Rights Reserved.