デルタ-シグマADC使用時における電源ノイズ影響の低減:アナログ設計のきほん【ADCとノイズ】(最終回)(3/4 ページ)

具体的な設計例を用いて、引き続き電源ノイズについて考察します。また、電源ノイズを低く保つベストプラクティスと、システムの総ノイズ特性を改善するデバッグのヒントについても説明します。

周波数プランニング

電源ノイズの低減に使用できるもう1つの手法では、スイッチングレギュレーターかADCのどちらかに周波数プランニングを利用します。第11回で説明し、図1にも再掲したように、ADCの電源はそれぞれ異なるPSRR特性を示す可能性があります。それに加えて、ADCのすべての電源は、デジタルフィルターの遮断帯域内の周波数でPSRRが急増します(図1参照)。デルタ-シグマADCでは、このデジタルフィルター応答が変調器周波数(fMOD)の倍数で繰り返されます。したがって、スイッチングノイズが変調回路周波数かその倍数に近い場合、このノイズはADC通過帯域に折り返すことになるかもしれません。

これらの信号が折り返さないようにしてシステムのPSRを改善するためには、可能であれば、フィルタのNULLのうちのどれか(通常は出力データレートの倍数)に当たるスイッチング周波数を選択してください。図11に、一般的な種類のADCフィルターの遮断帯域を示します。図11の左図は広帯域有限インパルス応答フィルター、右図はSINCフィルターです。ADCのデータレートはシステム要件により固定されているのが普通なので、赤の矢印で指した領域が、デジタルフィルター応答に基づいてスイッチング周波数に推奨される帯域です。データレートは自由に変えられるが、スイッチング周波数は固定されている場合に、その周波数がNULLとなるようなADCの出力データレートを選択してください。

LDOの追加

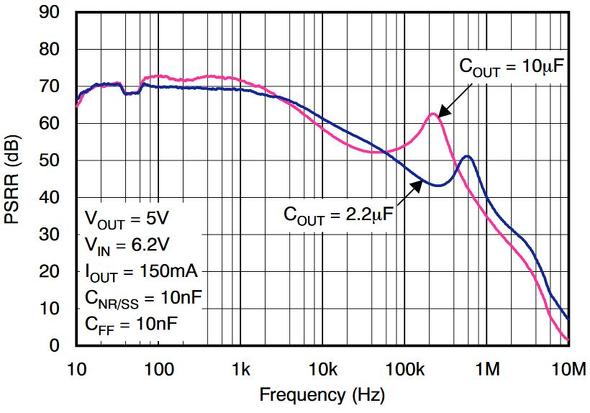

この記事の最初のセクションで説明したように、LDOを追加して不要なノイズを抑制することで、システムのPSRRをさらに改善できます。システムでスイッチング電源を使う予定である場合は、システムに最適な効果が出る特定のスイッチング周波数も検討してください。この手法は、すべての高分解能ADCアプリケーションに利用可能ですが、ノイズが結合したり出力に折り返したりしやすい広帯域アプリケーションでは、より重要です。この場合は、使用予定のスイッチング周波数での電源除去が最も大きいLDOを選択してください。あるいは逆に、LDOのPSRRがグラフで最高になる範囲のスイッチング周波数を検討してください。図12は、LDO『TPS7A49』(TI製)で、PSRRを周波数に対してプロットしたものです。このLDOのPSRRは、スイッチング周波数が高くなると減少することに注目してください。

Copyright © ITmedia, Inc. All Rights Reserved.