半導体(7) ―― MOSFETのゲート駆動回路の注意点(2):中堅技術者に贈る電子部品“徹底”活用講座(66)(1/3 ページ)

今回はパワーMOSFETの構造とそれに起因する寄生容量について説明するとともに、引き続きゲート駆動回路を中心にした使い方の注意事項を説明します。前回の記事と併せて読んでいただければ理解も深まると思います。

前回はパワーMOSFETのゲート駆動回路の注意事項について説明しました。表題に“MOSFET”が抜けていたことに加えてパワーMOSFETの構造の説明を後回しにしましたので前回の説明の中心となったゲート電極周辺の寄生容量の振る舞いについては分かりにくい面があったかと思います。今回は説明を後回しにしたパワーMOSFETの構造とそれに起因する寄生容量について説明するとともに、引き続きゲート駆動回路を中心にした使い方の注意事項を説明します。前回の記事と併せて読んでいただければ理解も深まると思います。

パワーMOSFETの構造

MOSFETには小信号用のMOSFETと電力用のパワーMOSFETがありますがここで採り上げるのは電力用のパワーMOSFETです。

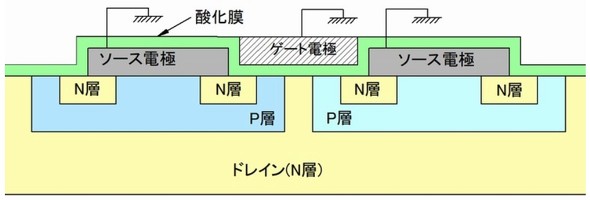

この種のMOSFETは図1に示すようにN形の基盤の中に縦方向にP形の拡散→N形の拡散を行います(N-ch MOSの場合)。MOSFETはこの構造に着目して2重拡散形MOSFETと呼ばれる時や、電流の流れる方向に着目して縦型MOSFETと呼ばれる時があります。

この構造によってゲート電位を0Vにした図1の場合にはソース電極に接続されたP層とドレインのN層は逆方向になり導通しないので高電圧に耐えることができます。

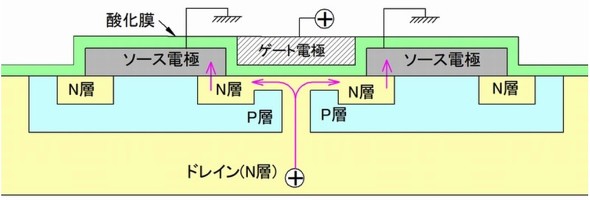

一方、図2のようにゲート電位に正の電圧を与えるとゲートの正電位に引かれてP層中の電子がゲート電極近傍に集まってきます。

電子が集まってきたこの領域はP層でありながらも電気特性は電子過多の状態、すなわちN層と同様の特性を示すようになります。この現象をP層のN反転と称します。

N反転した部位はソース電位のN層とドレインのN層とつながり、ドレインからソースまで電流パスが形成されます。この状態がMOSFETの導通状態です。この電流パスにはP層がないのでバイポーラトランジシタのような遅れ現象はなく、抵抗性の物性となって高速動作が可能になります。

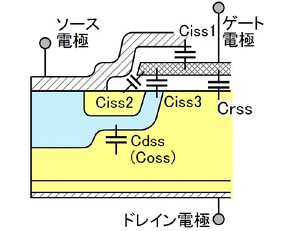

図3:MOSFETの寄生容量

※Wikipedia:Power MOSFETのFig. 4: Location of the intrinsic capacitances of a power MOSFET.を基に作成

【各部の寄生容量】

パワーMOSFETの各部位は図1に示すようにPN接合や酸化膜などによって分離されています。したがってこれらの面には図3に示すように寄生容量が発生(付随)します。これらの値はカタログなどに記載されていますがゲート〜ソース間容量Cissはゲート電極周辺のCiss1、Ciss2、Ciss3の合計値です。またドレインに付随する容量は電界の影響を強く受けるのでCrss、CdssなどはVdsによる電圧非直線性が強く現れます。

Copyright © ITmedia, Inc. All Rights Reserved.