半導体(7) ―― MOSFETのゲート駆動回路の注意点(2):中堅技術者に贈る電子部品“徹底”活用講座(66)(2/3 ページ)

今回はパワーMOSFETの構造とそれに起因する寄生容量について説明するとともに、引き続きゲート駆動回路を中心にした使い方の注意事項を説明します。前回の記事と併せて読んでいただければ理解も深まると思います。

ゲートの負信号による制御ICの誤動作

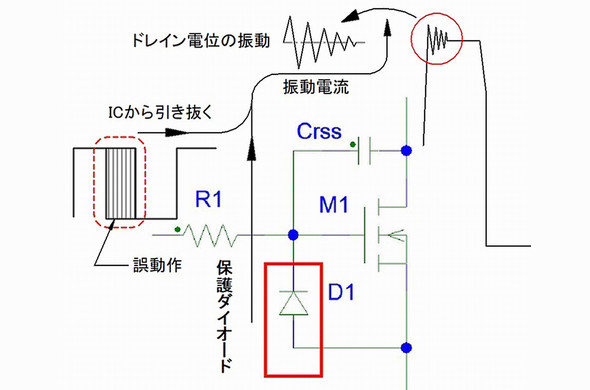

シングルエンド形スイッチング電源*においてL負荷のスイッチング動作を行うと、MOSFETのゲート端子にはチップ内部の寄生容量を通じてさまざまな振動が誘起されて、図4に示すように制御ICから電流が引き抜かれることがあります。

例えばMOSFETのターンオフ(ゲート電位=L)時、各部の寄生成分によってMOSFETのドレインに高周波のリンギングが発生します。この時Crssを通じて振動電流が制御IC〜Crss間を流れ、この振動電流の負成分によって制御IC内部の寄生トランジスタが動作してLレベルのはずのゲート駆動信号がHレベルになったり振動したりする現象を生じる時があります。

対策としては図4のように保護ダイオードをゲート〜ソース間に接続します。VFの差および、R1による電流制限によって制御ICの誤動作を防止できます。保護ダイオードにはVFの低いSBDが適していますが高温時の漏れ電流が小さい品種を選択してください。

*シングルエンド形:主として1石式のスイッチング電源の型式を指し、フィード・フォワード形、フライバック形、RCC形、などが含まれます。

一方、ハーフ(あるいはフル)ブリッジ形コンバーターはダブルエンド形と呼ばれます。ただし同じ2石式でもPushーPull型は独自の型式になります。

MOSFETの並列駆動の問題点

スイッチング電源の大電力化に従ってトランスを駆動するパワーMOSFETも1個のMOSFETでは定格オーバーになり複数個のMOSFETを使用せざるを得なくなります。

複数個のMOSFETを使う場合、回路方式をハーフブリッジやフルブリッジ構成、あるいはPush-Pull構成にするのも1つの方法です。しかし、制御の考え方を大幅に変更する必要があります。

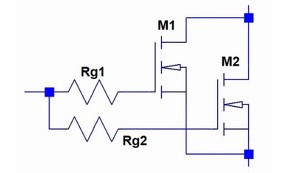

残る方法としては今回採り上げるように制御ICはそのままに、図5に示す複数個のMOSFETを並列駆動する方法があります。

MOSFETの場合、オン抵抗が正の温度特性を持つために図5のように単純に2個のMOSFETを並列に使用してもオン期間中の電流バランスは問題ありません。しかし、過渡時は下記のようにゲートの感度を示す特性値Vth(ON)*によってMOSFET(M1、M2)の電流バランスが崩れるために対策が必要になります。

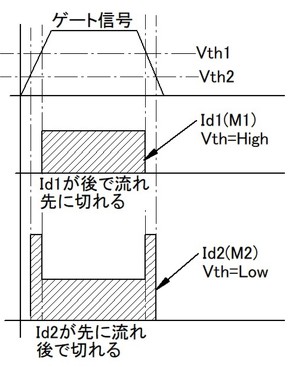

並列接続されたMOSFET間では図6に示すように、Vthのレベルが低い(高感度)方のMOSFETが早く導通して遅く遮断されます。したがってVthのバラツキはVthの低いMOSFETに過渡的な電流が集中することに直結します。

たとえ、この電流のピーク値が保証ドレインピーク電流IDPの範囲内に収まっていても損失のアンバランスはチャネル温度の差となって故障率にも影響します。

この電流のアンバランスは先に変化するMOSFETのゲート電荷の充放電に制御ICの電流が集中して使われて他方のMOSFETの動作が遅れることによって強調されます。電流アンバランスを軽減するには次のような対策が有効であり、設計の目安はId2のピークがM2のピーク電流保証値(IDP)に対して所定のマージンが取れるようにします。

- Vthを選別し±10mV程度に揃ったペア品を使用する。

- 図5中のRg1、Rg2はM1、M2への制御電流の集中を防ぎVthのアンバランスの影響を緩和するためのものです。抵抗値としては4.7〜22Ω程度でId1、Id2を確認しながら抵抗値を決定します。

注)上記の数値は定格ゲート電圧が10V品のものです。4V品では並列接続をするケースはほとんどありません。

*Vth(ON):Ids=1mAになる時のゲート電圧。文脈上Vthと略される時があります。

Copyright © ITmedia, Inc. All Rights Reserved.