半導体(10)―― MOSFETのアバランシェ不良:中堅技術者に贈る電子部品“徹底”活用講座(69)(2/3 ページ)

今回はアバランシェ耐量を使う時のマージンの取り方やアバランシェ保証導入初期にメーカーとともに経験した失敗事例について説明します。ここで紹介する失敗事例は現在では全て対策が取られ、同じ不良は発生しないはずです。

アバランシェ検査の失敗事例

次に紹介する失敗事例はアバランシェ保証導入初期に筆者らと半導体メーカーがともに学んできた失敗事例です。

アバランシェ試験機の接点不良

アバランシェ検査は極端に言えば破壊検査です。破壊するのに十分なエネルギーがFETに印加されなければ破壊は起こりません。

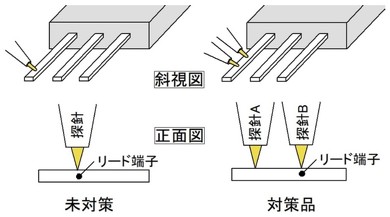

図2に示す事例はFETの試験機のプローブ(探針)が接触不良となったために破壊を起こすのに十分なエネルギーがFETに供給されず、検査をすり抜けて当方の工程で検出されたものです。

【対策】

探針を二重化し、探針A、B間でリード端子を介して導通を確認するようにしました。3本のリード全てで導通を確認した後に本来のアバランシェ検査に移行するのでエネルギー供給の確実性を上げることができます。

ガードリング(GR)の耐圧不良

ガードリング(GR)とは

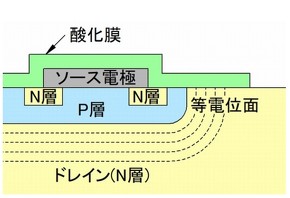

ガードリング(あるいはField Limiting Ring)とは高耐圧の半導体に見られる特有の構造です。

図3に示すようにMOSFETの最外周のセルは隣接する構造がないわけですからオフ時の等電位面はP-N接合の界面に沿って曲がりながらチップ表面に到達します。つまりP-N接合が表面に現れた箇所の電界強度は基本的に素子の内部と同じレベルになります。

チップ表面は酸化膜などの保護膜でカバーされていますので一定の耐圧は確保できますが他材料との界面ですのでチップ内部の空乏層の絶縁レベルには遠く及びません。つまり、このままではチップ表面の絶縁が素子の耐圧を決めるということになり、素子の特性を100%活用できないことになります。

表面電界強度の緩和策として図4に示す最外周のP-N接合の外側にガードリングと呼ばれるP+層*を埋め込むことが行われます。このフローティングされた埋め込みP+層の効果によって等電位面は横方向に伸ばされて集中は緩和されます。その結果、表面電界強度は低下して内部耐圧とバランスをとることができるようになります。

また一般に250V以上の高耐圧の半導体ではガードリングが持つ耐圧限界をチップ耐圧より10%程度高く設計します。これはチップ耐圧が10%程度バラつくことを前提にしたものです。

【不良現象】

社内受入検査のアバランシェ検査後にリーク電流(IDSS)が増加する現象が見られました。開封してチップ表面観察を行ったところ、ガードリングの耐圧不良と思われるリーク痕が見られました。

またメーカー見解も同様であり、ガードリングの耐圧とチップの耐圧のバランスがとれていないことが直接的な原因と分かりました。

アバランシェ対応のMOSFETはチップのブレーク電圧を管理できるようにチップをデザインしています。例えば500V品なら静的ブレーク電圧を505V〜520V程度に設計しますがこのままではチップのダイナミックインピーダンスによって動的ブレーク電圧がガードリングの耐圧(550V)を越える可能性があります。

このためガードリング部でフラッシュオーバーが起こり、リーク電流が増大したものです。

【対策】

ガードリングの耐圧を600V品に対応したものに変更しました。チップ内部の耐圧はアバランシェに対応していますので内部でブレークしてもダメージは残りません。

*:P+は高濃度P層

ガードリング(GR)はGR間の耐圧とN層〜GR間の耐圧のバランスを考慮して設計されます。

Copyright © ITmedia, Inc. All Rights Reserved.