半導体(10)―― MOSFETのアバランシェ不良:中堅技術者に贈る電子部品“徹底”活用講座(69)(3/3 ページ)

今回はアバランシェ耐量を使う時のマージンの取り方やアバランシェ保証導入初期にメーカーとともに経験した失敗事例について説明します。ここで紹介する失敗事例は現在では全て対策が取られ、同じ不良は発生しないはずです。

誤ったエネルギー吸収モード

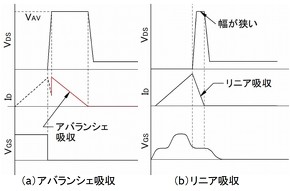

ここまで説明してきたように、アバランシェによるエネルギー吸収は図5(a)に示すように必ずMOSFETがオフの状態で行われます。

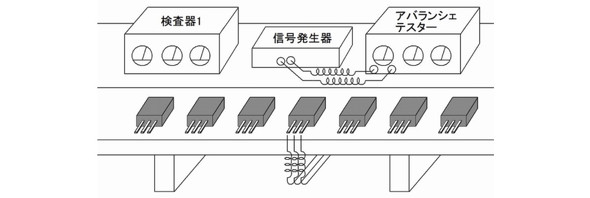

実際の検査工程のイメージを図6に示します。アバランシェ試験の試験条件は検査ステージの近傍に置かれた信号発生器から出力される信号で制御され、アバランシェテスターと呼ばれる専用の試験機を介してDUT(Device Under Test)に信号やエネルギーが加えられます。

しかしテスターからDUTまでの距離が長いと配線インダクタンスがFETの入力容量と時定数を構成し、図5(b)に示すようにDUTに加わる信号がなまって矩形波でなくなります。

この図5(b)の動作はこのようにゲート波形がなまったためにMOSFETが完全にオフにならずソースのP層にチャネルが形成された(リニア動作)ままアバランシェ動作が並行して起きてエネルギーを吸収しています。つまりブレークしなければならないアバランシェダイオードと並列にオンしているMOSFETが接続された構成になっていますのでブレーク期間が理論値より大幅に短くなっています。またアバランシェダイオード部に100%のエネルギーが印加されていないことになります。

このような試験条件でMOSFETが検査されたために当方の工程で20〜30%の不良を出したものです。この不良率のレベルはアバランシェ未対応品のレベルに近いものです。さらに複数回検査機を通しても不良率は低減すれども“0”にはならず、試験のダメージが残ることが推定されたため根本的にアバランシェ機構に対応していないものと判断せざるを得ませんでした。

(アバランシェ対応品の検査不良率は通常1%以下)

このような状況の背景には次の要因がありました。

- 半導体メーカーでは当然のことながら開発試作→工場試作→量産試作と数量レベルを上げていくわけですが開発から工場へ条件を引き継ぐ最初のステップ時に図6の設備名と信号発生器の設定条件のみを工場へ引き継いだために実際の各部の波形を確認していませんでした。

- さらに工場では試験機の配置を量産に適したレイアウトに変更したためにDUTへの配線が図6に示すような片道1m程度の長いレイアウトになっていました。

- 加えて工程レイアウト変更後のチェックも最初に開発部署から引き継いだ設定条件と動作波形の有無の確認のみで波形の妥当性チェックを行っていませんでした。

【対策】

- 当方の立ち合いのもと、信号発生器の設定変更と検査波形の確認を行い、アバランシェテスターの動作を確認しました。

- 基本的にアバランシェ保証に対応していないことが明確になったので認定を取り消し、使用禁止にしました。

その後、メーカーとしてアバランシェ保証品の新規(再?)開発に取り組むことになりましたが、再認定までには10年近い歳月がかかりました。また次の改善も行われました。

- 工程のレイアウト変更を行い、無駄な配線を短縮し、正しい波形を印加できるようにしました。

- 工場引き継ぎの資料情報に動作波形を追加し、工場側で波形を再現し、その確認をもって引き継ぎの情報とするようにしました。

- 工場試作時に開発部が立ち合い、開発部が意図した検査が行われているかを確認するようにしました。

- 動作波形を全数モニター上に標準波形と同時表示し、異常を目視でも判断できるようにしました。

今回の失敗事例は1つのメーカーに偏って起きているわけではありません。万全を期しているはずの各半導体メーカーで実際に起きた事例ですので新しい機能を保証する検査体制には経験の積み重ねが必要だということが分かるかと思います。

また説明してきた失敗事例は基本的にはメーカー内部のノウハウとして扱われ、基本的には業界内に情報は拡散していきません。

ただし、アバランシェテスターの改良バージョンの販売や筆者らの品質監査資料のチェック項目が増えることで各メーカー間に品質情報が伝搬・流布された結果として検査のレベルアップが図られ、今ではほとんどの半導体メーカーでこの種の不良は発生しないと思います。

つまり、このように不良事例は各半導体メーカーにとってはそれぞれ経験値が1つ上がるだけにしか過ぎませんがユーザーにはここで説明できるような多数の経験や情報が集まってきます。

連載第61回「半導体(2)-−実際に経験した不良と対策(I)」で述べたように「経験はユーザーにこそ溜まっていく」ということなのです。

今回はアバランシェ保証導入初期にメーカーとともに経験した失敗事例について説明しました。次回は新しいアバランシェ検査の考え方について説明します。

再び品質に関する話になりますが前回の記事の中で「不良は検査で取り除けばよい」との考え方の是非を評論しましたがこれは「検査時に不良になっていないと取り除けない」ことの裏返しです。

例えば前回の記事の中で「半殺し」の言葉を使いましたが、このように著しく残存寿命が短い製品が紛れ込んだ場合は検査で取り除くことはできません。しかし市場に出された製品は出荷後「あっ」と言う間に寿命が尽きて不良になります。つまり顧客にとっては不良品の流出と何ら違いがないのです。

この記事に関係した話になりますが前回の記事公開の23日前に納品された日本メーカー製の冷蔵庫が記事公開の4日後(=公開時は正常稼働中)に故障し、新品交換になりました(稼働27日)。この話は作り話ではなく正真正銘、本当の話です。

まさに「検査で不良品は取り除けない」を地でいくことになりました。

執筆者プロフィール

加藤 博二(かとう ひろじ)

1951年生まれ。1972年に松下電器産業(現パナソニック)に入社し、電子部品の市場品質担当を経た後、電源装置の開発・設計業務を担当。1979年からSPICEを独力で習得し、後日その経験を生かして、SPICE、有限要素法、熱流体解析ツールなどの数値解析ツールを活用した電源装置の設計手法の開発・導入に従事した。現在は、CAEコンサルタントSifoenのプロジェクト代表として、NPO法人「CAE懇話会」の解析塾のSPICEコースを担当するとともに、Webサイト「Sifoen」において、在職中の経験を基に、電子部品の構造とその使用方法、SPICE用モデルのモデリング手法、電源装置の設計手法、熱設計入門、有限要素法のキーポイントなどを、“分かって設計する”シリーズとして公開している。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

半導体(7) ―― MOSFETのゲート駆動回路の注意点(2)

半導体(7) ―― MOSFETのゲート駆動回路の注意点(2)

今回はパワーMOSFETの構造とそれに起因する寄生容量について説明するとともに、引き続きゲート駆動回路を中心にした使い方の注意事項を説明します。前回の記事と併せて読んでいただければ理解も深まると思います。 半導体(1) ―― 半導体の製造工程

半導体(1) ―― 半導体の製造工程

今回からは電子回路に欠かせない半導体について説明します。本シリーズでは半導体の市場不良および、その原因を説明するための製造工程の問題を主眼に説明をしていきます。 共振子(1) ―― 水晶デバイスとは

共振子(1) ―― 水晶デバイスとは

今回からはマイコンや各種発振器、フィルターに使われる共振子について説明していきます。これらの共振子は回路的には完成度が高く、指定された使い方を間違えなければ正しく動作します。発振器として市販されている部品もありますので適材適所で使い分けることが肝心になります。 電気二重層キャパシター(1) ―― 概要と原理

電気二重層キャパシター(1) ―― 概要と原理

今回からはキャパシターの一種である電気二重層キャパシター(EDLC)について説明していきます。EDLCは、耐圧は低い(数ボルト以下)のですがその容量はファラド(F)単位になり、大容量と言われるアルミ電解コンデンサーの数百倍から数千倍のエネルギー密度になります。 サーミスタ(1) ―― NTCサーミスタとPTCサーミスタ

サーミスタ(1) ―― NTCサーミスタとPTCサーミスタ

今回から「サーミスタ」を取り上げます。サーミスタの分類について簡単に説明するとともに、サーミスタを使用した回路動作の概要について解説していきます。第1回は、NTCサーミスタとPTCサーミスタの違いとともに、NTCサーミスタによる突入電流制限回路について考察します。 フェライト(1) ―― 磁性

フェライト(1) ―― 磁性

“電子部品をより正しく使いこなす”をテーマに、これからさまざまな電子部品を取り上げ、電子部品の“より詳しいところ”を紹介していきます。まずは「フェライト」について解説していきます。