半導体(11)―― MOSFETの新しいアバランシェ検査法:中堅技術者に贈る電子部品“徹底”活用講座(70)(1/3 ページ)

今回は今まで説明してこなかったアバランシェ検査の新しい考え方について説明します。

前回はアバランシェ保証導入初期にメーカーとともに経験してきた失敗事例について説明しました。それらの記事でお分かりかと思いますがアバランシェ検査に関する不良が複数の半導体メーカーで発生しましたので次のようにアバランシェ保証の認定基準を改訂しました。

【アバランシェ保証の認定監査】

半導体メーカーに対する技術的信用を見直し、必ず使う側自らの目で工程検査の状況を監査すること。部品認定までの時間的制約により現場監査を実施できない海外メーカーの場合には監査に該当する資料の提出をもって仮認定とし、後日確実に現場監査を行うこと。

注)アバランシェ検査は破壊検査であり、100%の確実性が求められます。使う側として経験的、品質的に納得できるレベルにあるか、否かの確認のために監査するようにしたものです。

今回は今まで説明してこなかったアバランシェ検査の新しい考え方について説明します。

新しいアバランシェの検査法

150℃でのアバランシェ試験

今まではブレーク期間中にTch=150℃、Id(dc)を成立させる前提で説明してきましたがもう1つの考え方にチャネル温度がTch(MAX)になるまでId(dc)のドレイン電流を流して過熱し、その後ターンオフさせてブレークすることでTch=150℃、Id(dc)を成立させる考え方もあります。

ただし、この場合Tchが試験中に150℃を超えるので使用材料も含めて170℃程度に耐える設計をしないと信頼性を保証することができません。試験条件の確認と共に使用材料(モールド樹脂、高温はんだなど)の確認を行ってください。

高速アバランシェ試験

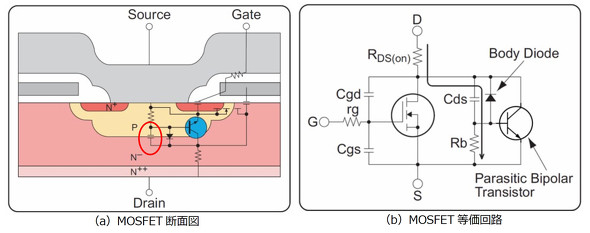

図1(a)にMOSFETの基本セルの断面図を示しますがドレイン(N層)−ソース(P層)間はアバランシェダイオードを構成すると共に接合容量Cds(赤丸部)を構成します。その等価回路を図1(b)に示しますがこの容量Cds流れる電流はダイオードを通る電流と共にベース短絡抵抗Rbを流れます。

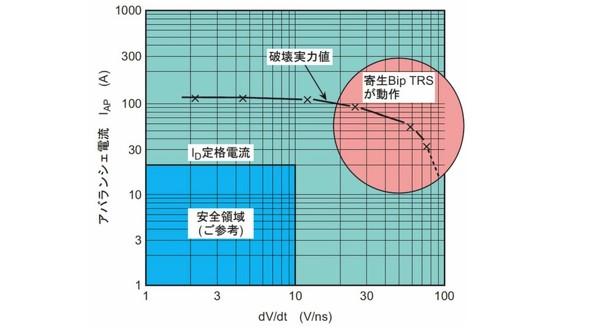

したがってVdsの立ち上がりが早いとCdsを流れる充電電流が増大し、アバランシェダイオードを流れる電流に対して無視できなくなりますので寄生トランジスタがターンオンしやすくなります。つまりドレイン電圧Vdsの立ち上がり速度(dV/dT)はアバランシェ能力に影響します。この様子を図2に示しますがこの例では20V/ns以上で破壊電流の低下が見られます。

近年のスイッチング電源の高周波化に伴い、Vdsの立ち上がりも高速化してきています。アバランシェ試験時のdV/dTを記載、提出してもらい、吸収エネルギーと共にdV/dTのマージンを確認する必要があります。

なお、この低下の様子は開発年次やシリーズによって異なり、高速品ほど低下の様子は改善されています。新しく開発されたシングルエンド形コンバーター用MOSFETシリーズのVDSS=500V〜900Vの品種では高速アバランシェの試験条件として10V/ns以上の値が保証されているMOSFETも多く量産されています。

この場合、MOSFETのターンオフ時間は50ns(500V品)〜90ns(900V品)より短くできません。またこのdV/dT規制は波形の始点〜終点間の平均値に適用されるものではなく、VDSの瞬時の変化率に適用されることに留意する必要があります。

Copyright © ITmedia, Inc. All Rights Reserved.