SLVSインタフェースをFPGAで活用せよ:低消費電力の差動伝送規格(2/3 ページ)

SLVSは、データ信号を高速かつ低消費電力で伝送する用途において、LVDSに替わって利用される機会が増加しているデータ伝送規格である。FPGAにSLVSを実装する場合には、LVDSを実装する場合とは異なるさまざまな知見が必要になる。本稿では、SLVSの概要と、FPGAにおける応用例を紹介する。

FPGAに実装する際の要件

FPGAを用いてSLVSとの互換性を持つ(SLVSコンパチブル)インタフェースを構築する際には、ターゲットとするFPGAデバイスの十分なハードウェアリソースの有無や、その入出力ポートがレシーバおよびトランスミッタの両方を実装できるだけの柔軟性の有無を検討しなければならない。

まず、SLVSのレシーバについては、外付け部品を用いることなくトランスミッタ出力端と直接接続できるよう、FPGAに差動終端が組み込まれていることが望まれる。また、FPGAのレシーバの多くがLVDSの使用を前提とした設計となっているので、接続対象となるFPGAレシーバの差動電圧およびコモンモード電圧の範囲が、SLVSの出力規格に適合していることを確認しておかなければならない。さらに、FPGAの差動出力ポートは、外付け部品を用いて構成される結合用の抵抗網により調整されるSLVSの出力電圧レベルに対して、必要な電流を供給できる必要がある。

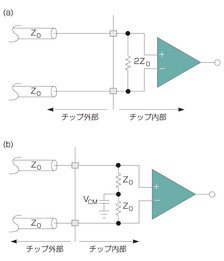

LVDSと同じく、SLVSもレシーバに終端負荷を必要とする。しかし、負荷をレシーバの内部に設置するか、外部に設置するかについては規定されていない。FPGAを用いて標準的なデバイスとのSLVSインタフェースを構築する場合、負荷の設置位置は両方とも利用できることがほとんどである。ノイズの少ない相互接続と堅牢なシステム動作を実現するには、FPGAレシーバに差動終端が組み込まれている方が有利である(図2)。

SLVSのトランスミッタに関しては、出力電流ソースのプログラマブル性が重要になる。差動駆動電流は、SLVS規格の要件を満足する値にプログラミングしておかなければならない。一方、差動振幅電圧とコモンモード電圧は、SLVSレシーバの要件に整合するように、通常は基板に搭載する外付け部品を用いた抵抗網を利用して調整する。基板搭載の抵抗網による電力消費を補うために、トランスミッタの電流ソースは、通常のLVDSで用いられる3.5mAよりも大きい電流をチップ外部の差動トレースに供給する必要がある。このような要件を満たす電流ソースとして、FPGAに従来から搭載されているLVDS互換の入出力ポートを利用することは通常は不可能だ。

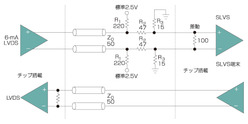

SLVSインタフェースのある実装例では、SLVSトランスミッタとしても利用可能なLVDS入力機能を備えたFPGAが用いられている(図3)。入力端ではいずれも内蔵の差動終端が利用される。コモンモード電圧および差動電圧の範囲はSLVSの規格を十分に満足しているので、基板に搭載する外付け部品を余分に用いることなく、2Gbpsに達する高速のデータ入力信号を受信することができる。このFPGAは、差動電流出力を2mA、3.5mA、4mA、6mAに設定することが可能であり。図3の例では、SLVSの規格に適合するよう、外付けの終端回路を利用した6mAの電流ソースが使用されている。この事例に適合するSLVSインタフェースの仕様の詳細を表1に示す。

Copyright © ITmedia, Inc. All Rights Reserved.