「Cortex-M0+」の動作時消費電力は「Cortex-M0」の2/3、処理性能は1.1倍:ARM Cortex-M0+

ARMのマイコン用プロセッサコアの新プロダクト「Cortex-M0+」は、「Cortex-M0」と同等以上の処理性能を確保しながら動作時消費電力を約2/3に低減した。また、マイコンシステム全体の消費電力を低減するためのアーキテクチャも導入している。

ARMは2011年3月、マイコン用プロセッサコアの新プロダクト「Cortex-M0+」を発表した(EE Times Japanの速報記事)。これまで「Flycatcher」という開発コードで呼ばれていたものだ。その名称から分かる通り、8/16ビットマイコンの置き換えを目指して2009年2月に発表された「Cortex-M0」の機能を拡張する形で再設計されたプロダクトである。命令セットとデバッガはCortex-M0と完全な互換性を備えているので、Cortex-M0向けに開発した組み込みソフトウェアをほぼそのまま利用できる。

Cortex-M0+とCortex-M0を比べると、「+」が付いたにもかかわらず処理性能の向上はあまり大きくない。動作周波数1MHz当たりの処理性能は、Cortex-M0が0.84DMIPS(1.62CoreMark)であるのに対して、Cortex-M0+は0.93DMIPS(1.77CoreMark)。10%程度の向上にとどまっている。

その一方で、各種センサー機器などの「Internet of Things(モノのインターネット)」と呼ばれる用途に合わせて、消費電力を大幅に低減したことが最大の特徴となっている。それも、プロセッサコアそのものの消費電力を低減するだけでなく、Cortex-M0+を搭載するマイコンシステム全体の消費電力を低減するためのアーキテクチャを導入しているのだ。

まずプロセッサコアについては、動作時の消費電力を低減した。TSMCの低消費電力の90nmプロセス「90LP」で製造したダイを50MHzで動作させた場合で比較すると、Cortex-M0の16.36μW/MHzと比べて、Cortex-M0+は約2/3となる11.21μW/MHzとなった。これは、パイプラインの段数を、Cortex-M0の3段から2段に減らしたことで実現した。パイプラインの段数は減ったものの、先述した通り処理能力は約1.1倍に向上している。

次に、マイコンシステム全体の消費電力の低減は、2つのアーキテクチャによって実現している。1つは、分岐先が決まるまでの待ち時間(Branch Shadow)を、最大でも2命令(1ワード)の間で終えるアーキテクチャだ。これによって、マイコンシステム全体の消費電力で大きな割合を占めるフラッシュメモリへのアクセス回数を減らせる。

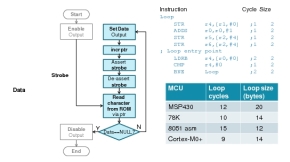

もう1つは、周辺回路へのアクセスに使う入出力インタフェース(I/O)を高速化した「シングルサイクルI/O」である。ARMが、Cortex-M0+と競合他社のマイコンのプロセッサコアについて、I/O制御のループサイクルとループサイズを比較したところ、Cortex-M0+の結果は極めて優れていた。これにより、低速動作時における周辺回路の動作時間を減らしたり、I/Oの制御を迅速に完了したりできるので、スリープモードに素早く移行することが可能になる。

また、Cortex-M0ではサポートしていなかった、より高機能のマイコン向けのプロダクトである「Cortex-M3」や「Coretx-M4」の機能を一部取り入れている。具体的には、メモリ保護ユニット(MPU)やベクターテーブルのリロケーション機能である。この他、Cortex-M0+で新たに追加された、Cortex-M0に無い機能としては、16ビット幅のフラッシュメモリへの対応や、SRAMの一部領域に格納した命令トレースを使ってデバッグを行う「MTB(Micro Trace Buffer)」などがある。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

低価格市場に侵攻する32ビットプロセッサ

低価格市場に侵攻する32ビットプロセッサ

低価格であることを求められる組み込み機器向けに、数多くの32ビットプロセッサが市場投入されている。その種のローエンド品は、8ビットや16ビットのプロセッサを代替することを目指して開発されたものだ。しかし、ローエンドの32ビット品と8ビット/16ビット品の比較検討を行う際には、価格に加えて、処理性能や消費電力、用途に対する適性などについても十分に調査する必要がある。 「2014年には75億台の機器市場が対象に」――ARM社が「Cortex-R」の展開を強化

「2014年には75億台の機器市場が対象に」――ARM社が「Cortex-R」の展開を強化

英ARM社は、高性能のリアルタイム処理が求められる用途向けのプロセッサコア「Cortex-Rファミリ」の展開を強化している。 ARM vs. Intel:プロセッサアーキテクチャの覇権はどちらの手に?(前編)

ARM vs. Intel:プロセッサアーキテクチャの覇権はどちらの手に?(前編)

現在、ARMとIntelによる、電子機器に用いられるアプリケーションプロセッサのアーキテクチャの覇権を賭けた争いが激化している。ARM陣営が、Intelのx86アーキテクチャが圧倒的シェアを占めるサーバー機器/PC市場への参入を果たそうとしている一方で、Intelをはじめとするx86陣営も、ARMの縄張りとも言える携帯電話機/タブレット端末市場への攻勢を強めている。