なぜいま、高速シリアル・インターフェイスなのか:高速シリアル・インターフェイス入門(1)(2/2 ページ)

全5回にわたり、昨今話題となっているUSB3.0やPCI Expressなどの高速シリアル・インターフェイス技術の概要をオシロスコープを使った計測という切り口で紹介します。

LVDS

Low Voltage Differential Signalingの頭文字であるLVDSは、ナショナル・セミコンダクタ社が開発したシリアル・インターフェイスの名前として知られていますが、その考え方は高速シリアル・インターフェイスに共通する基本的な概念を含んでいます。先ほどシリアル・インターフェイスにするとパラレル・インターフェイスよりも圧倒的に高速でデータ転送を行わなければならないと説明しました(SATA Gen1の場合はUltra ATA100の30倍)が、データ転送の高速化にはドライバの能力の問題を解決しなければなりませんでした。

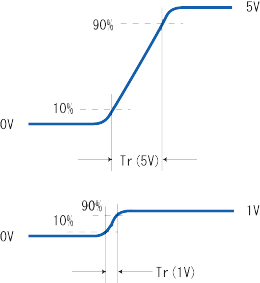

具体的にはドライバのスリューレイトを大きく上げることが難しかったのです。しかし、信号を小振幅にすることで速度を大きく向上させることができたのです。立ち上がり時間は、信号振幅の10%と90%のレベルで計測するというのが一般的ですが、同じスリューレイトであったとしても、図3に示したように振幅そのものが小さくなれば、それに比例して立ち上がり時間は短縮されるわけです。

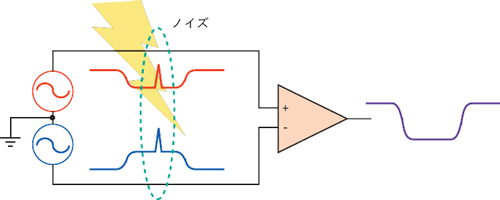

同じ半導体の技術を使っていても、単純にいえば信号の振幅を30分の1にすれば30倍の高速化が可能になるのです。しかしながら、高速化のために信号振幅を小さくするとノイズマージンが犠牲になります。ノイズの量が一定であれば、信号強度が小さくなるのでSN比が劣化するのは避けられないことです。それを、差動伝送を用いることで解決しました。

差動伝送とは、信号伝送に2本の線を用いておのおのに逆相の信号を送り、受信側で差分を受け取るというものです。図4で示したように信号は逆相で送られてきますが、ノイズは同相で乗ってくると考えられるので、受信側で差分を計算すれば信号は倍になるのに対してノイズ分はキャンセルされて大きく減衰するため、SN比を大きく向上できるようになります。

この結果、信号を小振幅にしてもSN比を高く保ち、良好の通信が高速で行えるようになります。また、差動にすると、ノイズの影響を受けないという利点があると同時に、外に対してもノイズを放射しにくいという利点があります。高速信号の場合にはスイッチング・ノイズを発散してしまう恐れがありますが、差動伝送の場合には、信号から生じる電磁界も逆相になっているので打ち消し合ってノイズの発散を抑える効果があります。

CRU

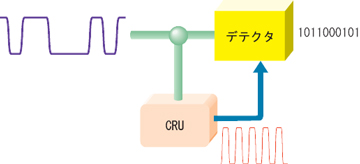

Clock Recovery Unitの略ですが、受信器で適切なクロック信号を再生する回路ブロックのことを指します。クロックの信号は、データ信号と別途送られてくる方式とデータ信号の中にクロック信号が埋め込まれている方式との2つがあり、それぞれにCRUが必要ですが、一般的なのはクロック信号がデータ信号に埋め込まれている方式です。この方式では、図5のように受信したデータ信号にCRUが接続され、埋め込まれたクロックの情報からクロック信号を作り出し、このクロックを基準にしてデータの判定を行います。

この方式ではデータとクロックがまったく同じ信号として送られてくるので、クロックとデータに時間差がありません。データにジッタが載ってタイミングが揺らいでいたとしても、適切にCRUを設計すれば、その揺らぎに従ってクロックを再生することができるので、結果的にタイミングの揺らぎは相殺されてタイミング・マージンが確保できるようになります。

このCRUは、PLLやDLLといった回路が利用されますが、信号のジッタ特性に合わせて適切に設計する必要があります。逆説的にとらえると、信号のジッタ特性は、CRUが想定する範囲の中になければならないということになります。つまり、同じジッタの特性であったとしても、ある規格で想定されているCRUの特性を基準とすると合格であっても、ほかの規格で想定されているCRUの特性を基準にすると不合格になるということも想定されます。

それほどCRUの特性はシリアル・インターフェイスの性能を左右するだけでなく、計測/評価で考慮しなければならない大きなファクターとなっています。

伝送線路

最後に、ギガヘルツを超える信号を取り扱う場合には、ケーブルやプリント基板なども単なる線とだけ扱うのではなく、マイクロ波を伝送する伝送路として考慮する必要が出てきます。これは取りも直さず、デジタル信号のアナログ的な振る舞いを頭に入れなければならないということです。デジタル信号で考えられてきたような「Highのレベルはどこで観測しても同じレベル」という前提は通用しません。あるいは、デジタル的な方形の波形はどこで観測しても同じ形という前提も通用しません。

反射などの現象も考慮しなければなりませんが、それよりもまず、信号が現実の伝送路を通るとき、減衰を受けて信号振幅が減少していきます。また、図6に示したようにその減衰具合は周波数が高くなるほど大きくなるため波形も変化します。もちろん、より理想的な特性の素材を使うことにより、減衰を抑えることもできますが、コストの面で難しいため、現行の素材であるガラスエポキシ系(FR4と呼ばれる素材が一般的)を用いて、その特性をいかにカバーしながら高速化を進めるかということが現在の技術的な課題となっています。

ここで簡単に紹介した技術をバックに、シリアル・インターフェイスの高速化が進められています。次回からは、実際の規格に沿って具体的な技術解説を行いたいと思います。

Copyright © ITmedia, Inc. All Rights Reserved.