SPICE応用設計(その5):不良率0とW.C.解析:SPICEの仕組みとその活用設計(16)(3/3 ページ)

今回から2回にわたって、これまで説明してきました「モンテカルロ解析」を補完し、併用する「ワーストケース解析」について説明します。

群内変動と群間変動、及び解析上の注意点

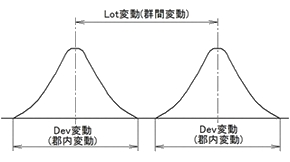

(PSpiceではLot変動→群間変動、Dev変動→群内変動に相当します)

図4に示すように任意の1つのロット(サンプル群)を採って測定した場合のデータの変動を群内変動(Deviation=Dev変動)といい、複数ロット(サンプル群)の平均値の変動を測定した場合のデータの変動を群間変動(Lot変動)といいます。

PSpiceにおいて部品の偏差欄に設定する偏差はDev偏差です。

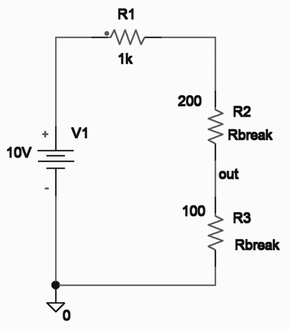

このような変動が指定された場合の解析の注意点について図5の回路を例に説明します。R1は偏差なし、R2、R3はDev偏差±5%、Lot偏差±10%とします。

理論解

R2〜R3の接続点out端子の電圧V(out)の最大値の理論解は次の通りです。

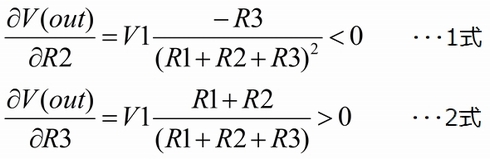

まず、R2、R3のそれぞれの感度を計算します。

次に、R2+R3を1つの抵抗群Rtとして考え、Lot変動の感度を計算します。

out端子電圧V(out)はRtの両端電位差を比率αで分圧したものとなります。このRtがV(out)に与える影響を1式、2式と同様に計算します。

実際の変動は3式に従ってR2、R3はLot変動として同じ方向へ同時に10%変化し、その中でのバラツキ(Dev)が5%になります。この場合は組み合わせを考えると表2の組み合わせが現実に起こり得る組み合わせです。(Nominal値は0.7692V)

決してLot+Devの変動巾が実際の変動巾になる訳ではありません。

| R2(0.9×0.95) | R2(0.9×1.05) | R2(1.1×0.95) | R2(1.1×1.05) | |

|---|---|---|---|---|

| R3(0.9×0.95) | 0.6804616 | 0.670851314 | −− | −− |

| R3(0.9×1.05) | 0.746740419 | 0.736268017 | −− | −− |

| R3(1.1×0.95) | −− | −− | 0.795584317 | 0.782478472 |

| R3(1.1×1.05) | −− | −− | 0.87202718 | 0.857779428 |

| 表2 実際の変動の組み合わせ | ||||

表2の結果から、V(out)が実際に取り得る値は0.872V(水色)で、単純な最悪値であるR2=Min/R3=Max(黄色)の10×115.5/(1000+171+115.5)=0.898Vにはなりません。

PSpiceではLot変動とDev変動を個別に設定できるのですが、残念なことにDev+Lotの総合変動は正常に動作していませんのでこのように設計者が操作・判断してやる必要があります。

どこで使うのか?

このような歪な偏った変動は理論上だけの話ではなく、具体的にはICの内部に生じます。ICの中では隣り合う素子(抵抗、半導体)間の相対精度は良好(±1〜5%)なのですが絶対精度は±20%以上です。hfeに至っては−50%〜+100%以上になる時もあります。

「IC内部の抵抗分圧回路に外部抵抗を直列接続して分圧比を調整するのは要注意」だと言われるのはこのような背景からです。そして、このような場合にはLot偏差に絶対精度を、そしてDev偏差に相対精度を割り付けて解析しなければなりません。また、半導体抵抗の温度特性も考慮する必要があります。

次回はLTspiceで公式にサポートされていないワーストケース解析の実行手順を説明すると共にワーストケース解析の落とし穴について説明していきます。

品質保証と品質管理

“「品質保証」は「品質管理」の結果にすぎない”とは昔から先達に言われてきた言葉ですが、ISOの導入につれて検査主体の保証になってきていると感じるのは私だけでしょうか?

例えて言うなら、品質管理は泉のわき水、品質保証は水道水であり、一度汚染された水はどれだけろ過しようが決してわき水の味に戻らないように、検査で不良品を排除できないモノがあることを理解すれば、「品質は管理すべき」と分かるはずです。QC用語なら品質管理は「予防保全」、品質保証は「事後保全」ともいえます。(注:水道水は十分に安全、かつ衛生的です)

また工程管理のアピール力としては、検査は改善の様子をグラフなどのビジュアルで表現できますが、品質管理は「不良が出なくて当たり前」なのでビジュアルに訴える力は弱いといえます。その面でも「除く検査」が安易に重宝されるのでしょうか?

執筆者プロフィール

加藤 博二(かとう ひろじ)

1951年生まれ。1972年に松下電器産業(現パナソニック)に入社し、電子部品の市場品質担当を経た後、電源装置の開発・設計業務を担当。1979年からSPICEを独力で習得し、後日その経験を生かして、SPICE、有限要素法、熱流体解析ツールなどの数値解析ツールを活用した電源装置の設計手法の開発・導入に従事した。現在は、CAEコンサルタントSifoenのプロジェクト代表として、NPO法人「CAE懇話会」の解析塾のSPICEコースを担当するとともに、Webサイト「Sifoen」において、在職中の経験を基に、電子部品の構造とその使用方法、SPICE用モデルのモデリング手法、電源装置の設計手法、熱設計入門、有限要素法のキーポイントなどを、“分かって設計する”シリーズとして公開している。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

SPICE応用設計(その1):パラメトリック解析

SPICE応用設計(その1):パラメトリック解析

これまでSPICEとはどのようなものかを紹介してきた本連載。いよいよ今回からは、SPICEというツールをどう設計に応用していくかを紹介してきます。今回は、オーディオアンプの設計を例にとりながら、「パラメトリック解析」の解説を行います。 SPICEモデルとライブラリ(その1)

SPICEモデルとライブラリ(その1)

設計した回路をSPICEで解析するには、使用している部品のSPICEモデルが必要だ。第10回では、このSPICEモデルについて解説する。 解析実行エラーの原因と対策(その1)

解析実行エラーの原因と対策(その1)

SPICEの解析を実際に行う際に問題になるのが「解析実行エラー」だ。第6回では、解析実行エラーの原因の切り分けや、主因である「収束エラー」について説明する。