静電気放電(ESD)対策

静電気放電(ESD:Electro-Static Discharge)対策とは、静電気放電に伴って発生した高電圧パルスが、半導体チップの内部回路を破壊したり、誤動作させてしまったりすることを防止する取り組みのこと。現在、半導体業界で主流になっているMOS(Metal Oxide Semiconductor)デバイスは一般に、静電気放電に弱い。入力ゲートに薄膜の絶縁体を利用しているからだ。ここに高電圧パルスが侵入すると絶縁破壊が発生し、最悪の場合、半導体チップが破壊されてしまう。

そこでESD対策では、半導体チップの内部回路に高電圧パルスが侵入しないように、その前段で高電圧パルスを除去する。具体的には、ダイオードやコンデンサ、フィルタなどを使って、高電圧パルスとともに流れ込む電流の高周波成分をグラウンドに流す。こうすることで、パルスの電圧をクランプし、高電圧が内部回路に印加されないようにする。

ESD対策は、以前から必要だったもので、今に始まったものではない。しかし、半導体チップの微細化とともに、ESD対策が難しくなっているのも事実だ。なぜならば、微細化に伴って、MOSデバイスを構成するトランジスタのゲート膜厚が薄くなっているからである。

さらに、扱う信号の周波数が高まっていることも、ESD対策の難易度向上に拍車を掛けている。前述のように、ESD対策では周波数の違いで、高電圧パルスを除去する。扱う信号の周波数が高くなると、信号と高電圧パルスの周波数成分が近くなる。この結果、高電圧パルスだけを除去するのが難しくなっている。光通信用ICやHDD(Hard Disk Drive)のリード・チャネルICなどでは、ESD対策回路の工夫が不可欠になっている。

帯電するモノと放電の経路が違う

半導体チップのESD耐性をテストする際に使用するモデルは複数ある。HBM(Human Body Model)や、CDM(Charged Device Model)、MM(Machine Model)などが代表的な例である。

それぞれのモデルで、帯電するモノと放電の経路が異なる。HBMは人体に帯電し、作業者が半導体チップに触れたとき、指を介して半導体チップに放電するというモデルである。MMは、製造ラインで使用する工具や治具などに帯電し、それらが半導体チップに接触したときに放電するというモデルだ。半導体テスタにおいて、プローブが端子に接触するケースがこれに相当する。MMは、HBMの最悪のケースという位置付けである。

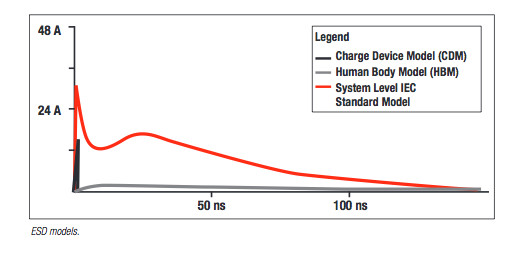

CDMは、電子機器の製造工程の中で、プラスチックの袋やトレイなどから滑り落ちたり、引きずられたりしたときに半導体チップ自体が帯電し、その後に製造工程で使用する装置の金属部に接触したときに放電するというモデルである。このモデルは、HBMやMMよりも対応が難しい。その理由は、放電によって発生する高電圧パルスの立ち上がり速度が極めて高いことにある(図1)。つまり、パルスの周波数が高いわけだ。立ち上がり速度は、HBMやMMよりも2桁程度高いとされている。

なお半導体デバイスのESD耐圧については、国際規格「IEC61000-4-2」が用意されている。この規格は、「静電気放電イミュニティ試験」に関するもので、半導体チップは必要に応じて、この試験をクリアする必要がある。例えばTIでは、ESD保護機能搭載USBホスト・ポート用電流制限スイッチ『TPD3S014』を提供している。

【関連リンク】

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2016年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.