ランダムなビット列を生成する回路:Design Ideas 信号源とパルス処理

従来のビット列発生器は、帰還をかけたシフト・レジスターを使って疑似ランダム・ビット列(PRBS)を得ていたため、有限長で同じパターンを繰り返すという問題を抱えていた。今回はこうした問題を打破できる、ランダム雑音を使って出力データ列を発生する回路を紹介する。

データ伝送システムの開発/評価において、ランダム・ビット列の発生器は必須である。この発生器を使えば、ビット誤り率や、ビット・パターンに依存する基線ゆらぎ、データ・ジッター、再生したクロック信号のジッターを測定できる。

従来のビット列発生器では、帰還をかけたシフト・レジスターを使って疑似ランダム・ビット列(PRBS)を得ていた。このため、このビット列は有限長で同じパターンを繰り返すという問題を抱えていた。

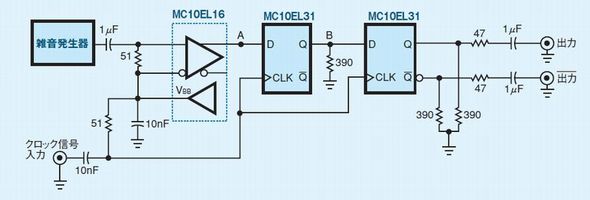

図1に示す回路を使えば、こうした問題を打破できる。ランダム雑音を使って出力データ列を発生する回路である。この回路は「ECLinPS」シリーズの標準論理ICを使う*1)。まずレシーバーIC「MC10EL16」で、入力した雑音信号をデジタル信号に変換する。次に最初のフリップフロップIC「MC10EL31」において、クロック信号の立ち上がりエッジで、デジタル信号をサンプリングしてランダムな出力信号を生成する。理想的には、これでランダムなビット列が得られる。

ところがこの方法では、フリップフロップへの入力データとクロック信号の立ち上がりエッジが同時に変化すると、フリップフロップがメタステーブル状態*2)に陥ってしまうという問題が生じる。この結果、出力が不確定になり、伝搬遅延時間が長くなってビット列にジッターが発生する*3)。

そこで、この問題を回避するために2番目のフリップフロップIC「MC10EL31」を用意した。1GHzまでのクロック信号を使った実験では、出力のアイ・パターンや周波数分布に異常は見られなかった。ECLinPSシリーズの標準論理ICは、超高速で動作するのでボード設計には注意が必要だ。回路の入出力は必ず50Ωで終端し、配線は最短距離で行う。それぞれのICには個別にバイパス・コンデンサーを接続する。

雑音源には、脚注4の参考文献の回路を使うことができる。雑音源の出力電圧は100mVrms〜1Vrms程度が必要。さらに、雑音源の周波数分布は少なくともクロック周波数まで必要になる。

*1)High Performance ECL Data、Motorola、1995.

*2)フリップフロップ回路のノードが、長期間、しきい値付近の電位にとどまってしまう現象。メタステーブル状態が発生すると、誤作動が起こるだけでなく、素子が劣化する原因にもなる。

*3)Metastability and the EC LinPS Family, Motorola Application Note AN1504.

*4)Sliwczynski、Lukasw、"Zener diode and MMICs produce true broadband noise,"EDN、p.158、Oct.14,1999.

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルタ回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバ】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事の中から200本を厳選し、5つのカテゴリに分けて収録した。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

パワーMOSFETを直流電子負荷に活用する

パワーMOSFETを直流電子負荷に活用する

太陽電池アレイやバッテリーなどの電源の試験に、電子回路によって構成した直流負荷を用いるが、市販製品は高価なものが多い。パワーMOSFETをリニア領域で用いると、電子負荷を自作できる。 電源コントローラICをパルス発生器として使う

電源コントローラICをパルス発生器として使う

スイッチングレギュレータ用コントローラICをパルス発生器として利用する方法を紹介する。立ち上がり/降下時間が2ns未満のゲート駆動用パルスを発生させることができるようになる。 PSoCで構成するディレイパターン生成器

PSoCで構成するディレイパターン生成器

デジタル回路、アナログ回路を問わず、実験などの目的でディレイパターンが必要となるケースは多い。このような状況に対応可能なものとして、筆者は1個のICでディレイパターン生成器を構成する方法を考案した。 パルス幅を電圧に変換する回路

パルス幅を電圧に変換する回路

今回は、パルス幅を電圧に変換する回路を紹介する。1つのパルス信号の入力が終わるまでの期間を直流電圧に変換する回路である。