デジタル方式のイコライザー「FFE」「DFE」の概要:高速シリアル伝送技術講座(12)(3/3 ページ)

民生機器の高速インタフェース(I/F)としても使われ始めたデジタル方式の信号補償技術であるFFE(Feed forward Equalizer)とDFE(Decision feedback Equalizer)について説明します。FFE/DFEの概要や動作の仕組みを紹介します。

DFE(ディシジョンフィードバックイコライザー)

DFEはDecision feedback Equalizer(判定帰還型イコライザー)の略語です。

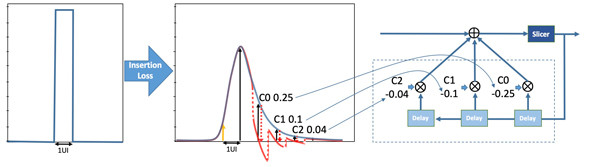

DFEは図6右のように出力側からフィードバックした信号に多段のディレイを挿入し、それぞれに係数を⊗部でかけ、⊕部で入力にフィードバックしすべて加算する方式です。

DFEブロック図のディレイはシリアルストリームの最大トグル周波数時間の1UIを一般的に使用しています。出力信号をフィードバックし順次ディレイを挿入し最後に加算(⊕部)しますが、タップ数(黒矢印の数)が多くなると複数のEYEをまたいだISIジッタに対して補償が可能になります。ただしFFEと同様にタップ数が増えるほど消費電力が大きくなります。

それでは図6でDFEの動作を説明していきます。図6左は送信端の波形です。送信端で1UIの幅の矩形波出力が、インサーションロスのある伝送路を通過した受信端では、図6中央に示した青の波形のように波形の傾きが緩やかになり、1UIを大きく超えていることが分かります。これがISIジッタとなります。

この1UIを大きく超えた緩やかな傾きの入力波形を、DFEブロック(図6右)では1UI単位のディレイでC0、C1、C2にそれぞれフィードバックし、⊗部でジッタの大きさの逆数(赤点線)をかけて入力に戻しています。その結果、出力は赤の波形になり、ISIジッタを低減しています。

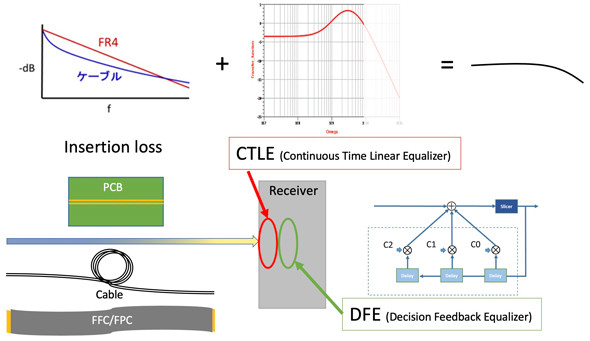

図7では受信デバイスでCTLEとDFEを使用した例を示しています。一般的に受信デバイスでは、CTLEの後段にDFEを実装し、まず前段で伝送路のローパスフィルター特性と逆特性(ハイパスフィルター)を持つCTLEにより伝送路によるISIジッタを低減させます。その後、後段のDFEで残りのISIジッタを低減します。

なお、図6のDFE後の波形(赤)を見ると分かりますが、黄色矢印のプリカーサ(前部分)で発生するISIジッタはDFEではキャンセルされずに残ります。

今回はデジタル方式のイコライザーのFFEとDFEについて説明しました。これらはディレイした複数の信号を組み合わせ、デジタル方式でも定常的に発生する伝送路のISIジッタを低減できることが理解できたのではないかと思います。この技術は今回例として取り上げた銅線伝送路のローパスフィルター特性だけでなく、任意の周波数特性で発生するISIジッタにも対応が可能な技術です。

次回は高速の信号伝送で重要となる特性インピーダンスの概念について説明していきます。

参考文献

・National Semiconductor LVDS Owner’s Manual Rev 3 and 4

・DesignCon 2016, 25G Long Reach Cable Link System Equalization Optimization Xilinx Inc.

筆者Profile

河西基文(かわにし もとふみ)/ザインエレクトロニクス シニアエキスパート

ナショナルセミコンダクタージャパンやジェナムジャパンなど、25年にわたり高速通信系半導体の製品開発・サポートおよびマーケットの開拓に従事。伝送路を含んだ半導体の高速設計手法が確立されていない時代に、LVDSオーナーズマニュアルの作成など、同マーケットの成長・普及に寄与してきた。

現在は日本のSerDes製品開発の先駆者的存在のザインエレクトロニクスで、プロダクトマーケティング・開発支援や人材育成などを行っている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

伝送路の特性とシグナルコンディショナーによるジッタの補償

伝送路の特性とシグナルコンディショナーによるジッタの補償

今回は伝送路の減衰特性によるジッタ、伝送路の最適な設計方法、半導体デバイスによるジッタの補償とその仕組みについて説明していきます。 高速シリアル伝送におけるジッタの種類とその特長

高速シリアル伝送におけるジッタの種類とその特長

前回は高速シリアル伝送で使用されるSerDes(シリアライザ・デシリアライザ)について説明しました。今回はSerDesなどの高速シリアルI/Fで、波形測定の際に観測されるジッタの種類とその特長について説明していきます。 PCIe、USB、Ethernet、HDMI、LVDSなど高速伝送技術の基本を理解するために

PCIe、USB、Ethernet、HDMI、LVDSなど高速伝送技術の基本を理解するために

本連載では、さまざまな高速通信規格に使用されている物理層の仕組みや性能、SerDesの機能や特徴とその種類、高速伝送での主要なパラメーター、伝送路を含んだ技術や設計手法などを分かりやすく解説していく。 差動信号伝送のメリット ――使用されている技術と注意点

差動信号伝送のメリット ――使用されている技術と注意点

高速シリアル伝送技術について基礎から学ぶ本連載。2回目は、差動信号伝送の特徴、メリットに焦点を当て、使用されている技術や注意点について解説していきます。 高速伝送の代表的な物理層 LVDS・PECL・CML

高速伝送の代表的な物理層 LVDS・PECL・CML

今回は、高速差動伝送で使用されている代表的な物理層である「LVDS」「PECL」「CML」の特長、接続方法、用途例を紹介していきます。 接続形態(トポロジ)と特性インピーダンス

接続形態(トポロジ)と特性インピーダンス

今回は接続形態(トポロジ)、特性インピーダンスについてです。LVDS系テクノロジーのさまざまなトポロジとその基本な構成、またPECLやCMLを使用して同機能を高速で実現する方法などについて紹介します。