NoC(Network-on-Chip)こそがSoCである:NoCとは(1)

NoC(Network-on-Chip)とはどのようなものか。これから複数回にわたり考察していきます。

「ネットワークこそがコンピュータである」。1984年にSun MicrosystemsのJohn Gage氏が作り出したこの言葉は、今となっては信じがたいほど先見の明に富んでいたことが証明されています。この考えが今、SoC(System-on-Chip)の領域で、再び台頭しつつあります。単純な配線を介してではなく、スイッチ、プロトコルコンバーター、パケタイザーなどの複雑なネットワークエレメントを介して互いにやり取りし合うチップ内の機能は、1984年当時にキャビネット内またはルーム内でネットワークを経由して通信していたコンピュータ群とさほど違いません。

SoCが登場するまでは、ボード上のAとBを接続するにあたり、エンジニアは配線の束を介することでデータを移動できました。最大の懸念は、配線の長さを管理し、AとBで全く同じ通信プロトコルが使用されるようにすることでした。懸念はせいぜいそれくらいでした。重要な機能は全てコンピュートエレメント内にあり、それらの貴重なコンポーネント間の配線は簡単な設計作業でした。

配線からアクティブバスロジックへ

SoCのケイパビリティが向上するにつれ、ボード全体あるいはもっと大規模なシステムを単一チップに統合し、その全てをCPUまたはプロセッサ群で制御することが可能になりました。各CPUで実行されるソフトウェアがシステムを制御することで、複数の機能を柔軟に処理できるようになりました。Armのようなプロセッサプロバイダーからのソリューションが急速に普及し、IPプロバイダーを含めた他のサプライヤもすぐその後に続きました。最初は複数のインターフェースプロトコルを処理するためのペリフェラルIPを提供することから始まりました。その後、ワイヤレス通信、グラフィックスプロセッシング、オーディオ、コンピュータビジョン、AIのそれぞれに特化されたプロセッサへと進化していきました。オンチップのワーキングメモリ、キャッシュ、オフチップまたはオフダイのDRAMへのDDR(Double Data Rate)インタフェースなどもここに追加しておくべきでしょう。

いつでも高度なSoCに統合できる素晴らしい機能は数多くありますが、それらの機能はどうやって互いにやり取りするのでしょう? 直接1対1結線するわけにはいきません。そんなことをすればチップは配線で覆われてしまいます。CPUとメモリは次に何を処理すればいいのかを突き止めようとしてはうように速度を落とすでしょう。トラフィックは全てフロー制御されたハイウェイ経由でルーティングされる必要があります。もし、あるIPがCPUに話しかけたければ、もしくはCPUが特定のIPに話しかけたければ、ハイウェイに乗れるまで順番を待つ必要があります。

バスはもはやただの配線ではなくなりました。動作速度の異なるドメイン間を流れるサポートデータのキューイングを制御すると同時に、今何が入っていて、次に何を入れればいいのかを監視するロジックがありました。パイプラインレジスタの使用が、距離を広げつつもタイミング制約を満たすことに役立ちました。多くのインテグレーションチームはこれを、制御ロジック、多重化、レジスタ、FIFOキューを介して接続を織りなしていくことから「バスファブリック」と呼んでいました。

バスアーキテクチャの進化

こうしてバスファブリックのアーキテクチャが出来上がったため、目的ごとに異なるアーキテクチャを想定することが可能になりました。AMBAファミリだけでもいろんな種類があり、それぞれに独自の利点と制約があります。もちろん複雑なSoCにおいてもバスは必要です。ここで登場したのがNoC(Network-on-Chip)という全く異なるタイプのテクノロジーです。これはコンセプトからしてそれまでのものとは違い、インターコネクト通信と物理的トランスポートを密結合することがないため、いろいろと新しいアーキテクチャの選択肢が見えてきます。これらの選択肢の相対的利点については私の次のブログで詳しく説明したいと思います。

インターコネクトを通じた差別化

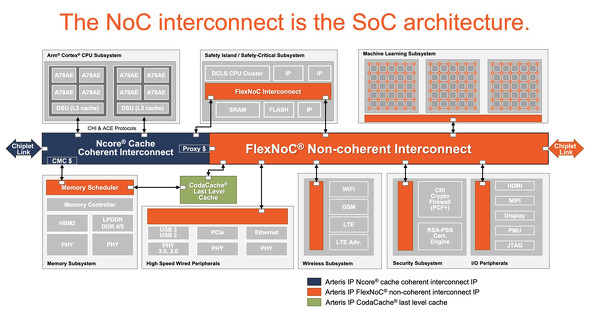

もう一つ考慮すべき重要なことがあります。今の典型的なSoCと言えば、数多くのサードパーティIPと、インテグレーターが優位性を持たせた独自IPとで構成されていることでしょう。しかしその優位性とはいかほどのものなのでしょうか? 競争者たちが同じサードパーティ製品を買えば買うほど、差別化の可能性は薄れていきます。したがって、設計チームがいかに効果的に自分たちのSoCを統合できるかが課題となってきます。幸い、それができるだけの余地は十分にあります。帯域幅、スループット、QoS(quality of service)、電力、安全性、コストはすべて統合によって決定づけられます。これらの要素は実装された通信アーキテクチャー――おそらくはNoC――によって影響されます。これについては次のブログで述べます。結局のところ、IPとオンチップ通信アーキテクチャーを慎重に選択することが競争力のあるチップを作ることにつながります。今やNoCこそがSoCなのです。

<次回(なぜNoCがクロスバースイッチに取って代わったのか)に続く>

【著:Benoit de Lescure/Arteris IP 最高技術責任者(CTO)】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

複雑なSoCでのタイミング収束を短期に済ませる秘訣

複雑なSoCでのタイミング収束を短期に済ませる秘訣

SoC設計は、ますます高度化し、物理的要因を考慮していないSoCアーキテクチャにより、甚大な被害が生じる事態も散見されるようになっています。そこでこれからのSoC設計で重要になるであろう“秘訣”をご紹介します。 ユニットレベルのクロックゲーティングで消費電力が下がる! モジュール方式のSoCインターコネクト

ユニットレベルのクロックゲーティングで消費電力が下がる! モジュール方式のSoCインターコネクト

SoCの低消費電力化で見過ごされがちな“インターコネクト”。ここでは、SoCのダイサイズを縮小し、消費電力を低減できるモジュール方式のSoCインターコネクト技術について紹介する。 32/64bitを追加した高性能MIPS Warrior CPU

32/64bitを追加した高性能MIPS Warrior CPU

イマジネーション・テクノロジーズは、MIPS Warrior CPUのラインアップに、組み込み32ビットMクラスCPU「M6200」「M6250」と64ビットPクラスCPU「P6600」を追加した。 SoCでもマルチコア化は進むのか?

SoCでもマルチコア化は進むのか?

サーバー機器向けのプロセッサは、1つのチップに複数のプロセッサコアを搭載する方向に進化している。この流れはしばらく継続することになりそうだ。では、これと同じ流れが、組み込み機器向けのSoCにも適用されるのだろうか。本稿では、SoCの進化の方向性について考察する。 Bluetooth 5に対応したマルチプロトコルSoCデバイス

Bluetooth 5に対応したマルチプロトコルSoCデバイス

シリコン・ラボラトリーズは、マルチプロトコル対応SoCデバイス「Wireless Gecko」シリーズを拡張し、新たに「EFR32xG12」シリーズを発表した。各種無線プロトコルに加えてBluetooth 5に対応している。