なぜNoCがクロスバースイッチに取って代わったのか:NoCとは(2)(2/2 ページ)

インターコネクト機能として単純なクロスバー方式を採用するという選択もあり得るでしょう。しかしシステム内のエレメントの数が増え始め、さらにエレメント間の距離が意図されたクロック周期に対して長くなってくると、クロスバーではもはやどうにもならず、NoC(Network-on-Chip)方式を採用する必要があります。

NoC(Network on Chip)の出現

インターネットにはこうした問題がありません。データはパケットに分割され、相互接続されたスイッチで構成される分散インフラを介して伝送され、適切なデスティネーションでリアセンブルされます。NoCはSoCレベルでこれと似たことをします。使用するのは軽量スイッチと、長距離伝送(SoC上で!)向けに最適化されたパケット化プロトコル、そして分散実装です。

図3:CPUと他のIPブロックのトランザクション(読み出し、書き込み、等)をNoCがパケットに変換し、これらのパケットがQoS、消費電力、ダイ面積、配線数等のSoC要件に最適化されたネットワークを介してルーティングされる (クリックで拡大)

カスケード化されたクロスバーによる通信トポロジの実装は「粒度の粗い」アプローチといえるかもしれません――。なぜなら、各クロスバーは大きなコンポーネントだからです。対して、それと同じ機能をNoSで実装することは「粒度の細かい」アプローチといえます。NoCでは、パケット伝送に必要なスイッチが非常にシンプルに(つまり、小さく、速く)なるようトランスポートプロトコルが選択されます。例えば、このプロトコルを使用することで個別のネットワークによる要求と応答の個別のトランスポートが可能になれば、スイッチは未処理トランザクションの追跡といった、要求ネットワークと応答ネットワークを組み合わせたクロスバーがしなければならないようなことを気にする必要がありません。そのため、同じ帯域幅で考えた場合、1個のNoCスイッチの規模は、未処理トランザクションの追跡に必要な全てのロジックを搭載する等価なAXIクロスバーの4分の1まで縮小できます。NoCは軽量であるため、最適化されたトポロジ内でスイッチを組み合わせることは、AXIクロスバーで同じことをやるよりはるかに簡単なのです。

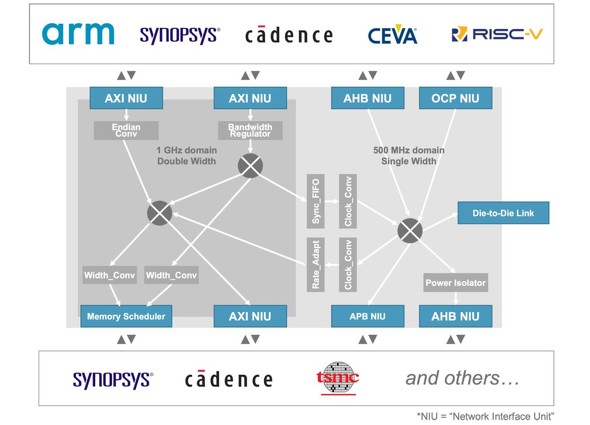

未処理(伝送中の)トランザクションの追跡は、当該NoCのNIU(ネットワークインターフェースユニット)の末端で1度だけ行われます(クロスバーの場合は、クロスバーカスケードの各クロスバーで行われます)。NIUは、IPブロックに使用されるトランザクションプロトコルをNoC内部トランスポートプロトコルに変換する役目を担っており、NoCでは非常に重要なコンポーネントです。このIPトランザクションプロトコルとNoCトラスポートプロトコルのデカップリングにより、NoCはトランスポートレベルでさまざまな「サービス」を実装することが可能になります。そしてこれらのサービスは、IPが通信に使用しているトランザクションプロトコルが何であろうと利用できます。例えば、トランスポートレベルでのパケット化とシリアル化により、そのNoCがカバーする長距離での混雑を軽減できます。2つの64ビット幅IPブロックは、認識することさえなく32ビット幅トランスポート経由で通信できるのです! クロックやパワードメイン、データ幅、バーストサポートなどのプロトコルケイパビリティをはじめとする他の調整もNoCで行えます。帯域幅や遅延制御、セキュリティ、セーフティ、デバッグなどのサービスは、全てNoCプロトコル上に実装されており、接続されている各IPに、それぞれのネイティブケイパビリティとは関係なく提供されます。

NoCと、そしてIPトランザクションプロトコルとNoCトランスポートプロトコルの変換に見るもう一つの利点は、元のSoCプラットフォームアーキテクチャから複数の派生チップ設計が作成されるプラットフォームベースの設計アプローチにおいて、従来よりもIPブロックを変更しやすくなることです。こうしたプラットフォームベースのSoC設計は、市場要件の変化により迅速に対応しつつ、設計のコストとリスクを減らしたいと考える企業が増えるにつれて徐々に広がりを見せています。もしSoC設計チームが、全ての接続コンポーネントを同一インタフェースに露出させなくてはならないクロスバーを採用していたら、IPブロックのエンドポイントで変更があった場合にその新しいコンポーネントをクロスバープロトコルにブリッジする必要が生じるでしょう。言い換えれば、内部の独立したトランスポートプロトコルを持つNoCを使用すれば、受信IPブロックトランザクションがパケットに変換される各エンドポイントを孤立できるため、SoCアーキテクチャに「プラグ・アンド・プレイ」で簡単に変更を加えられるのです。

大規模な設計だけではない

現在、大量生産されるSoCの接続はほとんどといってよいほどNoCアーキテクチャに基づいています。Arteris IPのNoCテクノロジを採用した良い事例の一つに、MobileyeのEyeQ ADAS SoCファミリーがあります(参考記事)。とはいえ、NoCはもっと小規模なチップにも有用です。パワードメインの数や派生/SoCプラットフォーム設計の要件が増えるにつれ、より小規模な設計においてもNoCが使用されている興味深い傾向が見られるようになっています。派生設計ファミリーを例にとりましょう。物理設計やタイミングクロージャを大幅に変更することなくIPを追加したり除外したりできるため、設計の再利用によるメリットを最大限に享受できます。また、パワーマネジメントについてはこの先でお話しますが、NoCテクノロジーを採用すれば、小型バッテリやMEMSによって電力供給されるIoTチップの超低消費電力を実現できるほど非常に高度な電圧/クロックドメインスキームを容易に作成できます。Texas InstrumentのIoT向けワイヤレスMCU、SimpleLinkファミリはその良い例(参考記事)で、NoC搭載システムの柔軟性、拡張性、IP再利用性が広く評価されつつあることを示しています。

<次回に続く>

【著:Benoit de Lescure/Arteris IP 最高技術責任者(CTO)】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

NoC(Network-on-Chip)こそがSoCである

NoC(Network-on-Chip)こそがSoCである

NoC(Network-on-Chip)とはどのようなものか。これから複数回にわたり考察していきます。 複雑なSoCでのタイミング収束を短期に済ませる秘訣

複雑なSoCでのタイミング収束を短期に済ませる秘訣

SoC設計は、ますます高度化し、物理的要因を考慮していないSoCアーキテクチャにより、甚大な被害が生じる事態も散見されるようになっています。そこでこれからのSoC設計で重要になるであろう“秘訣”をご紹介します。 ユニットレベルのクロックゲーティングで消費電力が下がる! モジュール方式のSoCインターコネクト

ユニットレベルのクロックゲーティングで消費電力が下がる! モジュール方式のSoCインターコネクト

SoCの低消費電力化で見過ごされがちな“インターコネクト”。ここでは、SoCのダイサイズを縮小し、消費電力を低減できるモジュール方式のSoCインターコネクト技術について紹介する。 32/64bitを追加した高性能MIPS Warrior CPU

32/64bitを追加した高性能MIPS Warrior CPU

イマジネーション・テクノロジーズは、MIPS Warrior CPUのラインアップに、組み込み32ビットMクラスCPU「M6200」「M6250」と64ビットPクラスCPU「P6600」を追加した。 SoCでもマルチコア化は進むのか?

SoCでもマルチコア化は進むのか?

サーバー機器向けのプロセッサは、1つのチップに複数のプロセッサコアを搭載する方向に進化している。この流れはしばらく継続することになりそうだ。では、これと同じ流れが、組み込み機器向けのSoCにも適用されるのだろうか。本稿では、SoCの進化の方向性について考察する。