“d—حٹا—‚ئ‹@”\ˆہ‘S‚إ‚àNoC‚ةڈں‚é‚à‚ج‚ب‚µپFNoC‚ئ‚حپi3پjپi2/2 ƒyپ[ƒWپj

“d—حٹا—‚â‹@”\ˆہ‘S‚ب‚ا‚±‚ê‚ـ‚إ‚جƒNƒچƒXƒoپ[ƒxپ[ƒX‚جƒCƒ“ƒ^پ[ƒRƒlƒNƒg‚إ‚حژہŒ»•s‰آ”\‚ب‹@”\‚ھپA‚¢‚©‚ةNoCپiNetworks-on-ChipپjƒeƒNƒmƒچƒWپ[‚ة‚و‚ء‚ؤ‰آ”\‚ة‚ب‚é‚©‚ة‚آ‚¢‚ؤچlژ@‚µ‚ـ‚·پB

ˆہ‘Sگ«‚ةٹض‚·‚é—v‹پ

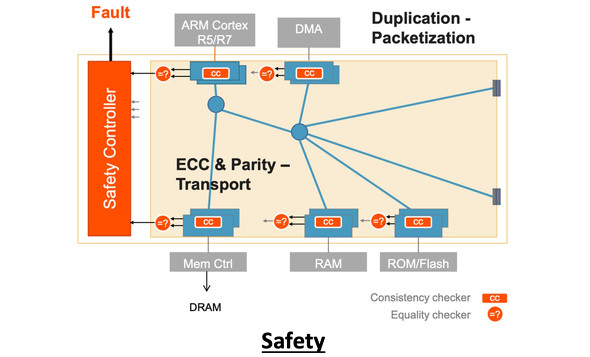

پ@‚ ‚éˆس–،‚إ‚حپAˆہ‘Sگ«‚ة‚آ‚¢‚ؤ‚à“¯‚¶‚و‚¤‚بگ}ژ®‚ھ“–‚ؤ‚ح‚ـ‚è‚ـ‚·پBIP‚ة‚آ‚¢‚ؤ‚حپAƒGƒ“ƒWƒjƒA‚½‚؟‚حˆہ‘SƒٹƒXƒN‚ًٹةکa‚·‚邽‚ك‚جƒeƒNƒjƒbƒNپiŒë‚è’ùگ³•„چ†پAƒpƒٹƒeƒBپAƒچƒbƒNƒXƒeƒbƒvپAژOڈdڈç’·چ\گ¬پj‚ًچl—¶‚µ‚ب‚ھ‚çˆہ‘S•ھگح‚ًچs‚¢‚ـ‚·پBƒCƒ“ƒ^پ[ƒRƒlƒNƒg‚ة‚آ‚¢‚ؤ‚ح‚ا‚¤‚ب‚ج‚إ‚µ‚ه‚¤پHپ@چ‚“x‚بNoCƒeƒNƒmƒچƒWپ[‚إ‚ح‚±‚ê‚ç‚ئ“¯‚¶ٹةکaƒIƒvƒVƒ‡ƒ“‚ھƒTƒ|پ[ƒg‚³‚ê‚ؤ‚¢‚邽‚كپANoC“à‚ة‚¨‚¢‚ؤ‚àIP‚¨‚و‚رپAƒTƒuƒVƒXƒeƒ€“à‚ئ‚ـ‚ء‚½‚“¯‚¶‚و‚¤‚ةŒجڈلƒ‚پ[ƒh‰e‹؟گf’f‰ًگح–ع•W‚ً’Bگ¬‚·‚邱‚ئ‚ھ‚إ‚«‚ـ‚·پB

پ@Fail-operationalپiŒجڈلژ“®چىŒp‘±پjگ«”\‚ھ—v‹پ‚³‚ê‚ؤ‚¢‚éASIL-Dڈ€‹’‚جگفŒvŒü‚¯‚ة‚ح‚³‚ç‚ة‹»–،گ[‚¢‹@”\‚ھ‚ ‚è‚ـ‚·پBFail-operational‚ة‚آ‚¢‚ؤپA‚±‚±‚إٹب’P‚ة•t‚¯‰ء‚¦‚ؤ‚¨‚«‚ـ‚·پBFail-operationalƒfƒoƒCƒX‚ح’لƒŒƒxƒ‹‚ج–â‘è‚ًٹؤژ‹‚µ‚ب‚¯‚ê‚خ‚ب‚ç‚ب‚¢‚¾‚¯‚إ‚ب‚پAپuچqچs’†پv‚جƒfƒoƒCƒX“à‚ة‚¨‚¯‚éIP‚جگ³ڈي“®چى‚ًŒںڈط‚إ‚«‚ب‚‚ؤ‚ح‚ب‚è‚ـ‚¹‚ٌپB–¢‰ًŒˆ‚ج–â‘è‚ھŒںڈo‚³‚ꂽڈêچ‡‚ة‚حپAŒë“®چى‚µ‚ؤ‚¢‚é‹@”\‚ًƒIƒtƒ‰ƒCƒ“‚ة‚µپA–â‘è‚ًƒhƒ‰ƒCƒoپ[‚ة•ٌچگ‚·‚éˆê•û‚إپAŒجڈل‚µ‚ؤ‚¢‚ؤ‚àˆث‘R‚ئ‚µ‚ؤژ©‘î‚ـ‚إ‚ج‘–چs‚ً‰آ”\‚ة‚µ‚ب‚‚ؤ‚ح‚ب‚è‚ـ‚¹‚ٌپB‚±‚ê‚حپAASIL-Dڈ€‹’‚ھ•s‰آŒ‡‚بگوگi‰^“]ژx‰‡ƒVƒXƒeƒ€‚âژ©“®‰^“]‹Zڈp‚إ—v‹پ‚³‚ê‚éپAگV‚µ‚¢ƒŒƒxƒ‹‚جˆہ‘Sگ«”\‚إ‚·پB

پ@Arteris IP NoC‚ح‚±‚جˆê’i‚ئŒµٹi‚ب—v‹پ‚ة‰‚¦‚ؤ‚¢‚ـ‚·پBگفŒv“à‚جIP‚حپAIP‚ًƒlƒbƒgƒڈپ[ƒN‚ةگع‘±‚µ‚ؤ‚¢‚éٹeƒlƒbƒgƒڈپ[ƒNƒCƒ“ƒ^پ[ƒtƒFپ[ƒXƒ†ƒjƒbƒgپiNIUپj‚إNoC‚©‚ç•ھ—£‚·‚邱‚ئ‚ھ‚إ‚«‚ـ‚·پB‚±‚ê‚ة‚ح“d—ح•ھ—£‚ج‚ئ‚«‚ئ“¯‚¶ƒپƒJƒjƒYƒ€‚ھژg—p‚³‚ê‚ؤ‚¢‚ـ‚·پB‚ذ‚ئ‚½‚ر•ھ—£‚³‚ê‚é‚ئپAASIL-Dڈ€‹’‚جˆہ‘SƒRƒ“ƒgƒچپ[ƒ‰‚ھ“–ٹYIP‚ة‘خ‚·‚éLBISTپiLogic Built-In Self-Testپjƒ`ƒFƒbƒN‚ًƒgƒٹƒKپ[‚µ‚ؤگ³ڈي“®چى‚ًŒںڈط‚µ‚ـ‚·پB–â‘è‚ھŒںڈo‚³‚ê‚é‚ئپA“–ٹYIP‚ح•ھ—£‚³‚ꂽ‚ـ‚ـپAˆہ‘SƒRƒ“ƒgƒچپ[ƒ‰‚ھ–â‘è‚ً•ٌچگ‚µ‚ـ‚·پB“–ٹYIP‚ھLBISTƒeƒXƒg‚ةچ‡ٹi‚·‚ê‚خپAچؤ“x—LŒّ‚ة‚µ‚ؤƒlƒbƒgƒڈپ[ƒN‚ة–ك‚·‚±‚ئ‚ھ‚إ‚«‚ـ‚·پBNoC‚ج‚±‚ج‹@”\‚ھ‚ ‚ê‚خپA‚±‚جƒŒƒxƒ‹‚ج•ھ—£‚ئƒeƒXƒg‚ھ‰آ”\‚ة‚ب‚è‚ـ‚·پB‚»‚à‚»‚àNoC‚ة‚ح•ھژU“I‚بگ«ژ؟‚ھ‚ ‚邽‚كپA‚·‚ׂؤ‚ھ—چ‚فچ‡‚ء‚ؤ‚¢‚邽‚ك‚ةگع‘±ƒRƒ“ƒ|پ[ƒlƒ“ƒg‚ج‚ا‚ê‚©ˆê‚آ‚إ‚àŒجڈل‚·‚é‚ئ‰ٌ•œ‚ة‘½‘ه‚بژٹش‚ً—v‚·‚éƒNƒچƒXƒoپ[‚ج‚و‚¤‚ب’†‰›ƒCƒ“ƒ^پ[ƒRƒlƒNƒg‚ة”ن‚×پAŒجڈل‚ة‘خ‚µ‚ؤ‚ح‚¨‚ج‚¸‚ئ‚و‚è—D‚ꂽٹو‹گ«‚ئ‘دگ«‚ًژہŒ»‚إ‚«‚ـ‚·پB

NoCƒeƒNƒmƒچƒWپ[‚حپAƒnپ[ƒhƒEƒFƒAƒxپ[ƒX‚جƒfپ[ƒ^•غŒى‚ً’ٌ‹ں‚µپASoC‚جگM—ٹگ«‚ئ‹@”\ˆہ‘Sگ«‚ًŒüڈم‚³‚¹‚éپmƒNƒٹƒbƒN‚إٹg‘هپn ڈoڈٹپFArteris IP

NoC‚ح‚·‚ׂؤ‚ًٹگ‚¦‚é

پ@NoC‚ھSoCƒCƒ“ƒ^پ[ƒRƒlƒNƒg•ھ–ى‚ًژx”z‚µ‚آ‚آ‚ ‚é——R‚ح‚à‚ح‚â–¾”’‚إ‚·پBژ„‚ح‚±‚جکAچع‚ج‘و1‰ٌ‹Lژ–‚إپAڈ¤—pIPژsڈê‚جگ¬’·‚ھپAƒfƒBƒtƒ@ƒŒƒ“ƒVƒƒƒuƒ‹‚بSoC‚ًچىگ¬پAچ\گ¬‚·‚邽‚ك‚جپu‚آ‚ـ‚ف‚ئƒ_ƒCƒ„ƒ‹پv‚ئ‚µ‚ؤNoCƒCƒ“ƒ^پ[ƒRƒlƒNƒg‚ھژg—p‚³‚ê‚éگ§Œن“_‚ًگ¶‚ف‚¾‚µ‚½‚ئگà–¾‚µ‚ـ‚µ‚½پB‚±‚ê‚ھپAژ„‚ج‚»‚ê‚ظ‚ا‘ه‚°‚³‚إ‚à‚ب‚¢پuNoC‚±‚»‚ھSoC‚إ‚ ‚éپv‚ئ‚¢‚¤ژه’£‚ة‚آ‚ب‚ھ‚ء‚½‚ي‚¯‚إ‚·پB‚³‚ç‚ةکAچع‘و2‰ٌ‚إ‚حپA‚¢‚©‚ةNoCƒeƒNƒmƒچƒWپ[‚ھپAƒTƒCƒY‚â•،ژG‚³‚ةٹضŒW‚ب‚‚ ‚ç‚ن‚éSoC‚جƒNƒچƒXƒoپ[ƒxپ[ƒX‚جƒCƒ“ƒ^پ[ƒRƒlƒNƒg‚ةڈں‚ء‚ؤ‚¢‚é‚©‚ئ‚¢‚¤‚±‚ئ‚ًگà–¾‚µ‚ـ‚µ‚½پB

پ@‚»‚µ‚ؤ–{‹Lژ–‚إ‚حپA“d—حٹا—‚â‹@”\ˆہ‘S‚ب‚اپA‚±‚ê‚ـ‚إ‚جƒNƒچƒXƒoپ[ƒxپ[ƒX‚جƒCƒ“ƒ^پ[ƒRƒlƒNƒg‚إ‚حژہŒ»•s‰آ”\‚ب‹@”\‚ھ‚¢‚©‚ةNoCƒeƒNƒmƒچƒWپ[‚ة‚و‚ء‚ؤ‰آ”\‚ة‚ب‚é‚©‚ئ‚¢‚¤‚±‚ئ‚ةڈإ“_‚ً“–‚ؤ‚ؤ‚«‚ـ‚µ‚½پBŒ‹‹ا‚ج‚ئ‚±‚ëپAƒ‚ƒ_ƒ“SoC‚ًچى‚ء‚ؤ‚¢‚éگفŒvƒ`پ[ƒ€‚ة‚ئ‚ء‚ؤ‚حپi‚»‚ê‚ھ‘ه‹K–حƒfپ[ƒ^ƒZƒ“ƒ^پ[‚جAIƒAƒNƒZƒ‰ƒŒپ[ƒ^‚إ‚ ‚낤‚ئپAگ₦‚¸ڈ—ت‚ج“d—ح‚ًڈء”‘±‚¯‚ؤ‚¢‚éIoTƒZƒ“ƒTپ[‚إ‚ ‚낤‚ئپjپASoCƒAپ[ƒLƒeƒNƒ`ƒƒ‚ًژہ‘•‚µپA“à•”‚جƒfپ[ƒ^ƒtƒچپ[‚ًچإ“K‰»‚·‚邽‚ك‚جŒ®‚ًˆ¬‚é‚ج‚حNoCƒCƒ“ƒ^پ[ƒRƒlƒNƒgƒeƒNƒmƒچƒWپ[‚¾‚ئ‚¢‚¤‚±‚ئ‚إ‚·پB

پy’کپFBenoit de Lescureپ^Arteris IP چإچ‚‹Zڈpگس”CژزپiCTOپjپz

Copyright © ITmedia, Inc. All Rights Reserved.

ٹضکA‹Lژ–

‚ب‚؛NoC‚ھƒNƒچƒXƒoپ[ƒXƒCƒbƒ`‚ةژو‚ء‚ؤ‘م‚ي‚ء‚½‚ج‚©

‚ب‚؛NoC‚ھƒNƒچƒXƒoپ[ƒXƒCƒbƒ`‚ةژو‚ء‚ؤ‘م‚ي‚ء‚½‚ج‚©

ƒCƒ“ƒ^پ[ƒRƒlƒNƒg‹@”\‚ئ‚µ‚ؤ’Pڈƒ‚بƒNƒچƒXƒoپ[•ûژ®‚ًچج—p‚·‚é‚ئ‚¢‚¤‘I‘ً‚à‚ ‚蓾‚é‚إ‚µ‚ه‚¤پB‚µ‚©‚µƒVƒXƒeƒ€“à‚جƒGƒŒƒپƒ“ƒg‚جگ”‚ھ‘‚¦ژn‚كپA‚³‚ç‚ةƒGƒŒƒپƒ“ƒgٹش‚ج‹——£‚ھˆسگ}‚³‚ꂽƒNƒچƒbƒNژüٹْ‚ة‘خ‚µ‚ؤ’·‚‚ب‚ء‚ؤ‚‚é‚ئپAƒNƒچƒXƒoپ[‚إ‚ح‚à‚ح‚â‚ا‚¤‚ة‚à‚ب‚炸پANoCپiNetwork-on-Chipپj•ûژ®‚ًچج—p‚·‚é•K—v‚ھ‚ ‚è‚ـ‚·پB NoCپiNetwork-on-Chipپj‚±‚»‚ھSoC‚إ‚ ‚é

NoCپiNetwork-on-Chipپj‚±‚»‚ھSoC‚إ‚ ‚é

NoCپiNetwork-on-Chipپj‚ئ‚ح‚ا‚ج‚و‚¤‚ب‚à‚ج‚©پB‚±‚ê‚©‚ç•،گ”‰ٌ‚ة‚ي‚½‚èچlژ@‚µ‚ؤ‚¢‚«‚ـ‚·پB •،ژG‚بSoC‚إ‚جƒ^ƒCƒ~ƒ“ƒOژû‘©‚ً’Zٹْ‚ةچد‚ـ‚¹‚é”éŒچ

•،ژG‚بSoC‚إ‚جƒ^ƒCƒ~ƒ“ƒOژû‘©‚ً’Zٹْ‚ةچد‚ـ‚¹‚é”éŒچ

SoCگفŒv‚حپA‚ـ‚·‚ـ‚·چ‚“x‰»‚µپA•¨—“I—vˆِ‚ًچl—¶‚µ‚ؤ‚¢‚ب‚¢SoCƒAپ[ƒLƒeƒNƒ`ƒƒ‚ة‚و‚èپAگr‘ه‚ب”يٹQ‚ھگ¶‚¶‚éژ–‘ش‚àژUŒ©‚³‚ê‚é‚و‚¤‚ة‚ب‚ء‚ؤ‚¢‚ـ‚·پB‚»‚±‚إ‚±‚ê‚©‚ç‚جSoCگفŒv‚إڈd—v‚ة‚ب‚é‚إ‚ ‚낤پg”éŒچپh‚ً‚²ڈذ‰î‚µ‚ـ‚·پB ƒ†ƒjƒbƒgƒŒƒxƒ‹‚جƒNƒچƒbƒNƒQپ[ƒeƒBƒ“ƒO‚إڈء”ï“d—ح‚ھ‰؛‚ھ‚éپI ƒ‚ƒWƒ…پ[ƒ‹•ûژ®‚جSoCƒCƒ“ƒ^پ[ƒRƒlƒNƒg

ƒ†ƒjƒbƒgƒŒƒxƒ‹‚جƒNƒچƒbƒNƒQپ[ƒeƒBƒ“ƒO‚إڈء”ï“d—ح‚ھ‰؛‚ھ‚éپI ƒ‚ƒWƒ…پ[ƒ‹•ûژ®‚جSoCƒCƒ“ƒ^پ[ƒRƒlƒNƒg

SoC‚ج’لڈء”ï“d—ح‰»‚إŒ©‰ك‚²‚³‚ê‚ھ‚؟‚بپgƒCƒ“ƒ^پ[ƒRƒlƒNƒgپhپB‚±‚±‚إ‚حپASoC‚جƒ_ƒCƒTƒCƒY‚ًڈkڈ¬‚µپAڈء”ï“d—ح‚ً’لŒ¸‚إ‚«‚郂ƒWƒ…پ[ƒ‹•ûژ®‚جSoCƒCƒ“ƒ^پ[ƒRƒlƒNƒg‹Zڈp‚ة‚آ‚¢‚ؤڈذ‰î‚·‚éپB 32/64bit‚ً’ا‰ء‚µ‚½چ‚گ«”\MIPS Warrior CPU

32/64bit‚ً’ا‰ء‚µ‚½چ‚گ«”\MIPS Warrior CPU

ƒCƒ}ƒWƒlپ[ƒVƒ‡ƒ“پEƒeƒNƒmƒچƒWپ[ƒY‚حپAMIPS Warrior CPU‚جƒ‰ƒCƒ“ƒAƒbƒv‚ةپA‘g‚فچ‚ف32ƒrƒbƒgMƒNƒ‰ƒXCPUپuM6200پvپuM6250پv‚ئ64ƒrƒbƒgPƒNƒ‰ƒXCPUپuP6600پv‚ً’ا‰ء‚µ‚½پB SoC‚إ‚àƒ}ƒ‹ƒ`ƒRƒA‰»‚حگi‚ق‚ج‚©پH

SoC‚إ‚àƒ}ƒ‹ƒ`ƒRƒA‰»‚حگi‚ق‚ج‚©پH

ƒTپ[ƒoپ[‹@ٹيŒü‚¯‚جƒvƒچƒZƒbƒT‚حپA1‚آ‚جƒ`ƒbƒv‚ة•،گ”‚جƒvƒچƒZƒbƒTƒRƒA‚ً“‹چع‚·‚é•ûŒü‚ةگi‰»‚µ‚ؤ‚¢‚éپB‚±‚ج—¬‚ê‚ح‚µ‚خ‚ç‚Œp‘±‚·‚邱‚ئ‚ة‚ب‚è‚»‚¤‚¾پB‚إ‚حپA‚±‚ê‚ئ“¯‚¶—¬‚ê‚ھپA‘g‚فچ‚ف‹@ٹيŒü‚¯‚جSoC‚ة‚à“K—p‚³‚ê‚é‚ج‚¾‚낤‚©پB–{چe‚إ‚حپASoC‚جگi‰»‚ج•ûŒüگ«‚ة‚آ‚¢‚ؤچlژ@‚·‚éپB