マイクロプロセッサを使用したシステム、回路設計時に重要なポイントは:マイクロプロセッサQ&Aハンドブック(3)(6/7 ページ)

マイクロプロセッサ(MPU)を使用したボードを開発するユーザーが抱えるさまざまな悩みに対し、マイクロプロセッサメーカーのエンジニアが回答していく連載「マイクロプロセッサQ&Aハンドブック」。今回は、「回路設計時の重要ポイント」について紹介します。

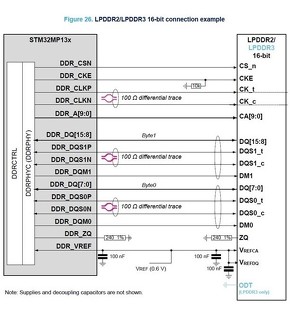

外付けRAMの接続回路

マイクロプロセッサでは、RAMが外付けとなります。RAMはDDRメモリを使用します。STM32MP1シリーズでは、外付けのRAMとして、DDR3、DDR3L、LPDDR2が使用可能です。DDR3とDDR3Lの違いは、電源電圧(1.5V対1.35V)とVREFレベル(0.75V対0.675V)のみです。

図8と図9に、それぞれDDR3LとLPDDR2の接続回路例を示します。

2x16ビットデバイスの場合、終端電圧(VTT)電源に接続されたインピーダンス整合抵抗ネットワークは、最後のデバイスのできるだけ近くに配置する必要があります。インピーダンスの不連続性を回避するには、「フライバイ」配線を使用する必要があります。

また、STM32MP1シリーズでDDR3、DDR3L、LPDDR2、LPDDR3を使用する場合には、次の外付け抵抗が必要になります。

DDR_ZQ(DDR3、DDR3L、LPDDR2、LPDDR3)

DDRのドライバーおよびODTのインピーダンス補正用に240Ω 1%抵抗をDDR_ZQとVSSの間に接続する必要があります。この抵抗は、各DDR3/DDR3Lコンポーネントで必要なZQ抵抗と共用しないでください。

CKE(DDR3、DDR3L、LPDDR2、LPDDR3)

CKEは、DRAMの内部回路とクロックを有効(レジスタをハイ)/無効(レジスタをロー)にするものです。10kΩのプルダウン抵抗が必要です。

DDR_RESETN(LPDDR2、LPDDR3)

DDR_RESETNは、DDRコントローラーからDDRデバイスへの非同期低速リセット信号です。10kΩのプルダウン抵抗が必要です。この信号は、パワーオン時またはリセットが必要なときにローになります。そうでない場合、信号はデフォルトでハイになります。

外付けフラッシュメモリの接続回路

外部ストレージとして、SDカード、eMMC、パラレルNANDフラッシュ、シリアルNORフラッシュ、シリアルNANDフラッシュを使用します。STM32MP1シリーズでは、それぞれの接続回路例がアプリケーションノート「AN5474」※5)に記載してありますので、そちらを参照してください。

※5)AN5474

Copyright © ITmedia, Inc. All Rights Reserved.