電流出力型DACの消費電力を抑える設計手法:電源電圧の動的制御がカギ(4/4 ページ)

本稿では、電流出力型のD-Aコンバーター(IDAC)の消費電力をできるだけ抑えるための設計手法を解説します。

基板設計の例

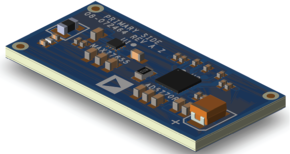

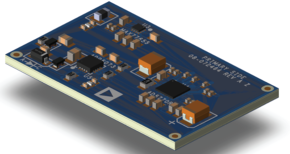

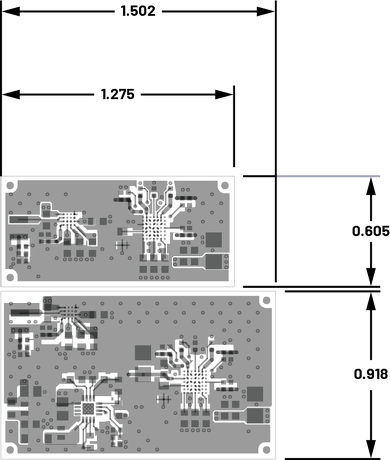

ハードウェアの実装方法としては、最終的なアプリケーションに応じてさまざまな形態が考えられます。図9(上)に示したのは、ユニポーラ電源を使用する場合の基板の設計例です。図9(下)は、バイポーラ電源を使用する場合の基板の設計例です。どちらの基板にも、マイコンの実装スペースは含まれていません。それぞれのサイズは1.275インチ × 0.605インチ(約32.4mm × 15.4mm)、1.502インチ × 0.918インチ(約38.2mm × 23.3mm)です。なお、これらはコンパクトなサイズを実現できることを示すために用意したものです。本稿で示した評価結果は別のボードを使用して取得しました。図10に、図9に示した両ソリューションの3次元のレンダリング結果を示します。

図9 電源ソリューションとしてSIMOコンバーターを使用した場合の基板レイアウト。(上)はユニポーラ電源、(下)はバイポーラ電源を構成した場合の例[クリックで拡大] 出所:Analog Devices

まとめ

DPCを利用すれば、電流出力型DACのチップ内で消費される電力量を低減できます。負荷の動作に悪影響を及ぼすことなく、トータルの消費電力を削減できるようになります。SIMOコンバーターは、IDACを駆動するための理想的なソリューションです。このタイプのDC-DCコンバーターを採用すれば、コンパクトな基板によって高い電力効率を達成することが可能になります。

著者プロフィール

Suraj Pai:Analog Devicesのプロダクトアプリケーションエンジニア。2017年にRV工科大学(インド・バンガロール)で電子/通信工学の学士号を取得。その後、高精度コンバータ・グループのアプリケーション・エンジニアとしてインド支社に入社。

Vikash Sethia:Analog Devicesのスタッフアプリケーションエンジニア。2018年に入社。高精度コンバータ・グループ(インド・バンガロール)でミックスド・シグナルICやSiPソリューションを含む高精度のD-Aコンバーター製品を担当。2001年にアッサム工科大学(インド・グワーハーティ)で電子/通信工学の学士号、2004年にインド工科大学(インド ポワイ)で電気工学の修士号を取得。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ビルのデジタル化を加速する 「シングルペアイーサネット」の役割とは?

ビルのデジタル化を加速する 「シングルペアイーサネット」の役割とは?

温室効果ガスの排出量を実質ゼロに抑える「ネット・ゼロ」を世界レベルで達成するためには、通信用インフラのデジタル化が必要不可欠です。本稿では、シングルペアイーサネットを導入することにより、ビルのデジタル化を図る方法について説明します。 インテリジェントエッジ向けのソフトウェア開発環境

インテリジェントエッジ向けのソフトウェア開発環境

アナログ・デバイセズは、エッジデバイス向けの組み込みソフトウェア開発環境「CodeFusion Studio」を発表した。Microsoftの「Visual Studio Code」をベースとし、IDEやSDK、生産性向上ツール、構成ツールを統合している。 デルタ-シグマADC内のノイズの概要

デルタ-シグマADC内のノイズの概要

デルタ-シグマADCのノイズに関する包括的な理解を深めるために、代表的なシグナルチェーンの一般的なノイズ源を調べ、ノイズを低減して高精度の測定を維持する手法を解説していきます。第1回は、ADCノイズの基本を重点的に見ていきながら、「ノイズとは何なのか」「高分解能ADCと低分解能ADCではノイズにどのような違いがあるか」などの疑問について、詳しく説明していきます。 電磁気学入門(16)生涯の悩みの種「電磁場適合性」

電磁気学入門(16)生涯の悩みの種「電磁場適合性」

電磁気学入門講座。最終回となる今回は、トランス設計者にとって生涯の悩みの種である「電磁場適合性(EMC)」について解説します。