ニュース

第5世代トレンチアシストプレーナーSiC MOSFET、Navitas:AIデータセンターなど向け

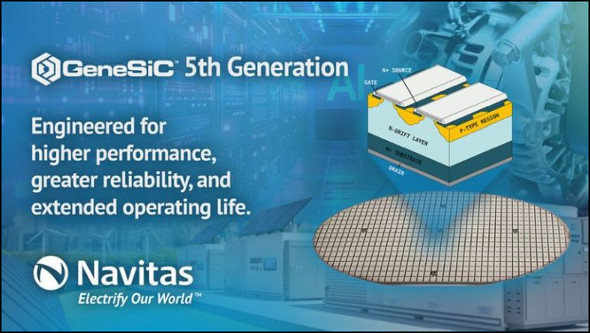

Navitas Semiconductorは第5世代「GeneSiC」プラットフォームを発表した。トレンチアシストプレーナー構造によって損失を低減し、高効率と高信頼性を実現するものである。

Navitas Semiconductorは、第5世代「GeneSiC」プラットフォームとして、高耐圧トレンチアシストプレーナー(TAP)炭化ケイ素(SiC) MOSFETを発表した。新しい1200V耐圧製品群は、第4世代GeneSiC技術に基づく超高耐圧の2.3kVおよび3.3kVデバイスを補完するものだとしている。

この最新世代は、これまでで最もコンパクトなTAPアーキテクチャを採用。プレーナゲートの堅牢性とトレンチ構造による性能向上を組み合わせることで、効率と長期信頼性を向上させている。AIデータセンター、電力網およびエネルギーインフラ、産業電化といった高電圧用途を対象としている。

従来の1200Vデバイスと比較して、新世代ではRDS(on)×QGDの性能指数が35%改善。スイッチング損失を低減し、より低温で高周波の動作を可能しhている。また、QGD/QGS比が約25%改善され、高いしきい値電圧を安定して維持することで、スイッチングの堅牢性を強化。高ノイズ環境における寄生ターンオン耐性を向上させている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Navitasが2.3kV/3.3kV SiC MOSFETを投入

Navitasが2.3kV/3.3kV SiC MOSFETを投入

Navitasは第4世代「GeneSiC」プラットフォームベースの2.3kVおよび3.3kVのSiC MOSFETのサンプル提供を開始した。 独自のトレンチアシストプレーナー(TAP)技術を採用し、エネルギーインフラ向けに高信頼性と高性能を実現する。 SiC/GaNデバイスは離陸間近

SiC/GaNデバイスは離陸間近

シリコン材料をベースとするパワー半導体と比べて、高速かつ低損失で動作する特性を備えているのが、SiCやGaNなどのワイドギャップ材料を用いた次世代のパワー半導体である。これまで、高いコストや歩留まりの低さなどによって、SiC/GaNデバイスの量産はなかなか立ち上がらなかった。しかし、2010年以降、複数のメーカーによる量産化の取り組みが加速している。 SiC MOSFETに対応可能、アバゴの高速ゲート駆動用フォトカプラ

SiC MOSFETに対応可能、アバゴの高速ゲート駆動用フォトカプラ

ACPL-P/W345とACPL-P/W346は、伝達遅延時間が最大120nsで同社従来品に比べて半分に短縮した高速ゲート駆動用フォトカプラである。出力ピーク電流は最大で1Aと2.5Aの製品がある。同相ノイズ除去(CMR)性能は最小50kV/μsを確保した。 独自トレンチ構造で電力損失半減 三菱電機のSiC-MOSFETチップ

独自トレンチ構造で電力損失半減 三菱電機のSiC-MOSFETチップ

三菱電機は、パワーエレクトロニクス機器向けに、「トレンチ型SiC-MOSFETチップ」のサンプル提供を開始した。オン抵抗とスイッチング損失を抑え、プレーナー型SiC-MOSFETと比較して、電力損失を約50%低減する。 EV充電向けのSiC MOSFETモジュール

EV充電向けのSiC MOSFETモジュール

オン・セミコンダクターは、EV充電ステーション向けの1200VフルSiC MOSFET 2パックモジュール「NXH010P120MNF1」「NXH006P120MNF2」を発表した。プレーナー技術を活用し、18〜20Vの駆動電圧に対応する。 SiCパワーMOSFETのスイッチング特性、大電流/高電圧領域の測定で解析精度が向上

SiCパワーMOSFETのスイッチング特性、大電流/高電圧領域の測定で解析精度が向上

SiCパワーMOSFETのデバイスモデルの精度向上には、「大電流/高電圧領域のId-Vd特性」および「オン抵抗の温度依存性」を考慮しデバイスモデルに反映させることも重要となる。今回はこの2点に関する解説を行う。