第55回 開発キットを今すぐ入手し、活用する!! 〜28nm「Stratix V」FPGAの価値を高める:FPGA Insights

「製品の価値を高めるために、より多くの時間を付加機能の開発に費やしたい」――多くのシステム設計者は常にこうした思いで開発に取り組んでいるに違いない。そのためには、旧来の設計工程を見直し、開発の効率を今まで以上に高めていく工夫をしていかなければならない。その有効な方法の1つが開発キットを活用することである。

開発キットの活用と開発効率の改善

日本のシステム開発は、どちらかといえばカスタム指向の設計が行われてきた。それは独自機能を商品に取り込み回路設計のノウハウなどを外部に漏らさないこと、さらには大量生産によるコストダウン効果、などを狙ったからだ。しかし、市場のニーズは多様化し、機器に求められる高機能化や高性能化のスピードは年々加速している。これを実現可能とするために半導体デバイス技術も、その微細化技術や高集積化技術は、業界が予測したスピードで進化を遂げている。これに対して、回路設計という視点から見れば、設計ツールの機能や設計のマンパワーが変革するスピードに十分に追い付いていけてないのが現状だ。このため、従来のシステムLSIを用いた回路設計だと、設計仕様や規格の変更などに柔軟に対応できなくなっている。

こうした中、日本企業が世界市場で商品の競争力を高めて行くには、開発の効率改善は大きなカギを握ることになろう。基本機能の開発期間をこれまでより短縮し、その分価値を高める機能の開発に集中していかなければならない。その上で開発コストも下げていく。このような開発効率の改善に向けて、FPGAを用いた回路設計が注目を集めている。本稿ではその一例として、アルテラが提供している「Stratix® V FPGA開発キット」を取り上げ、その概要や機能を紹介する。

最高クラスの性能とバンド幅を実現するStratix V FPGA

FPGAデバイスに求められる性能や機能は、実装するアプリケーションごとに異なる。コストの低減は共通した要求ではあるが、性能/機能と消費電力については、その両立が難しいケースもあり、目的(用途)に応じて優先度を決める必要がある。システム設計者にとって、設計要件に適したFPGAを検討するに当たって、その選択肢は広い方がよい。

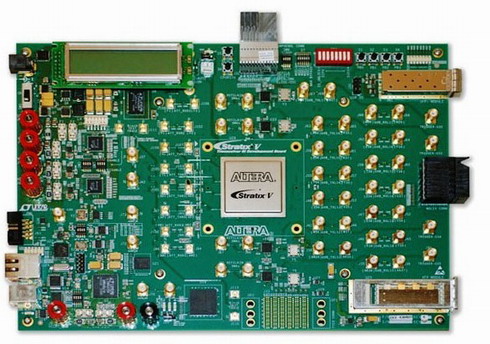

アルテラの28nm FPGA製品は、アプリケーションごとに異なる顧客の設計ニーズに対応していくために開発された。そして性能や搭載できる機能の違いによって3つのデバイス・ファミリで供給されている。その中でStratix V FPGA(図1)は、最高クラスのバンド幅を実現するとともに消費電力やコストを従来製品より抑えた、ハイエンドの28nm FPGA製品という位置付けである。

アルテラはStratix V FPGAファミリとして4種類を用意している。最大14.1Gbpsのトランシーバを内蔵した「Stratix V GX FPGA」、最大14.1Gbpsのトランシーバを内蔵するとともに、高いDSP処理能力を必要とする用途に適した「Stratix V GS FPGA」、28Gbpsトランシーバを用いる用途向けに最適化された「Stratix V GT FPGA」、952Kロジック・エレメント以上を集積した「Stratix V E FPGA」である。

Stratix V FPGAファミリに対して、現在は6種類の開発キットがアルテラから用意されている。これらの開発キットを用いると、さまざまなシステムの機能を開発・検査することができるため、設計時間の大幅な短縮を可能とする。例えば、OTN(光トランスポート・ネットワーク)や100Gイーサネットなど、高いバンド幅を必要とするシステムの開発ができるように最適化されている。

Stratix V GX FPGA開発キット

Stratix V GX FPGA開発キットは、直ちにFPGAの設計を開始するために必要となるハードウェアとソフトウェアを含む設計環境を提供する。PCI Express® Gen3に対応するシステムの設計と検証などを行うことができる。同開発キットには、Stratix V GX FPGAデバイスを搭載した開発ボード(図2)やボード回路図、「Quartus® II」開発ソフトウェアの開発キット・エディションなどが含まれている。

トランシーバ・シグナル・インテグリティ開発キット/Stratix V GXエディション&Stratix V GTエディション

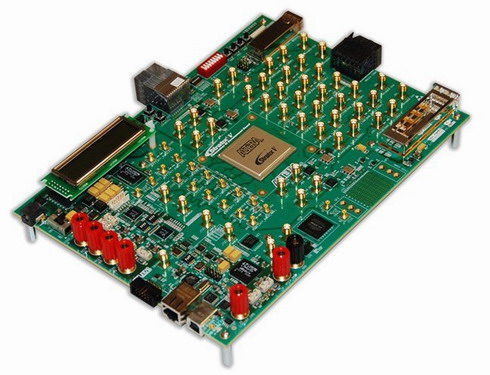

トランシーバ・シグナル・インテグリティ開発キット/Stratix V GXエディションとトランシーバ・シグナル・インテグリティ開発キット/Stratix V GTエディションのいずれも、電気的コンプライアンス・テストや相互接続性解析を行うための基盤となるものである。特に、Stratix V GXエディションでは600Mbps〜12.5Gbpsでのトランシーバ・リンク特性を、Stratix V GTエディションでは最大28Gbpsのトランシーバ・リンク特性をそれぞれ評価することができるなど、設計者は実環境でのシステム分析を行うことが可能である。これ以外にも、PRBS(疑似ランダム・バイナリ・シーケンス)パターンの生成とチェック、最適なビット・エラー・レシオ(BER)を得るためのリンク設定の微調整、などが可能である。開発ボードを図3(Stratix V GXエディション)と図4(Stratix V GTエディション)に示す。

100G開発キットStratix V GXエディション

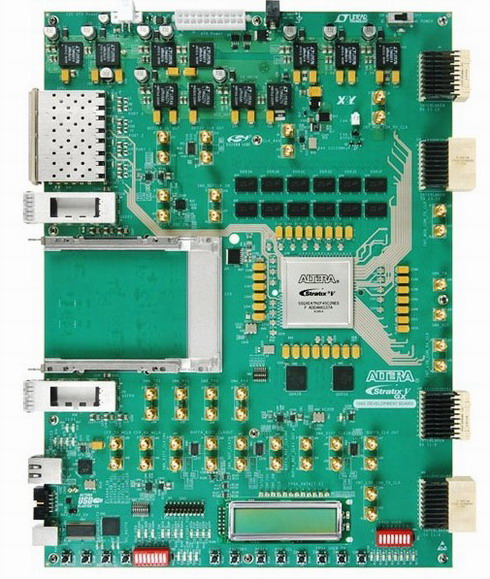

100G開発キットStratix V GXエディションには、各光モジュールに対応した10G/40G/100Gライン・インタフェース、DDR3メモリ・バンクとQDR II BL2メモリ・バンクによる外部メモリ・インタフェースなどが実装されている。これによって、最大12.5Gbpsのトランシーバ性能の評価、10G/40G/100GイーサネットやInterlakenといった規格に準拠しているかどうかの検証を行うことができる。開発キットを図5に示す。

DSP開発キットStratix V GSエディション

DSP開発キットStratix V GSエディションは、高いデジタル信号処理性能を必要とするシステム向けに有用であり、可変精度DSPを使ったStratix V GSを直ちに設計するために必要と思われる設計環境が提供される。開発ボードを図6に示す。

アドバンスド・システム開発キット

アドバンスド・システム開発キットは、最大8KのウルトラHD動画処理性能を実現するために十分なロジック・リソースやバンド幅を備えている。例えば、外部メモリ・スループットは1.5Tbps以上を達成し、バンド幅はPCIe® Gen3×16を実現している。しかも、ハードウェアだけでなく、高解像度ビデオ処理システムの開発に必要となるファームウェアやPCIeストリーミング・ドライバなども備えていることから、開発の生産性は格段に高まるものと思われる。

開発キットの活用と開発効率の改善

日本企業が世界市場で商品の競争力を高めて行くには、開発の効率改善は大きなカギを握ることになろう。基本機能の開発期間をこれまでより短縮し、その分価値を高める機能の開発に集中していかなければならない。その上で開発コストも下げていく。このような開発効率の改善に向けて、FPGAを用いた回路設計が注目を集めている。さらに、さまざまな開発キットがFPGAベンダーより、いち早く提供されることで、FPGAに対するシステム開発者の敷居も低くなり、その動きは一段と加速されることになろう。

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2014年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.