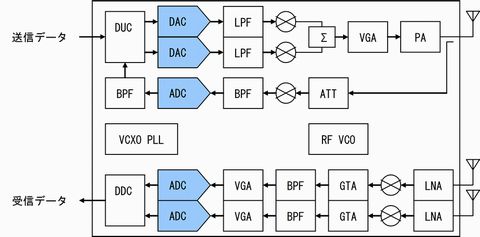

4G/LTE無線基地局などの通信機器をはじめとして、医療機器、計測機器などのアプリケーションにおいて、高速・高分解能のA/Dコンバータ、D/Aコンバータが数多く使われるようになっている(図1)。

これらのコンバータは、多くの場合、ボード上でFPGAなどの高速ロジック・デバイスとインターフェイスする。コンバータが高速・高分解能になるほど、接続に必要なデジタル信号は高速化し、信号線の本数が増える。従来のパラレル接続では、信号線の本数が多いためボード上のレイアウトが難しい、コンバータやFPGAの小型化が難しい、スキューやノイズなど特性の面でも問題を生じやすいなど、多くの課題を抱えていた。

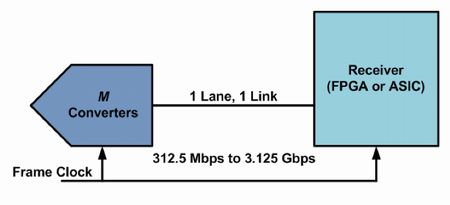

そこで、このような高速コンバータとFPGAなどの高速ロジック・デバイスをシリアル接続するための標準インターフェイスとして、JEDECによって策定されたのがJESD204規格である。8b-10b変換やスクランブラなど既存の高速シリアル・インターフェイス技術を利用し、かつデータ・コンバータ向けとして必要なスペックに最適化した規格となっている(図2)。

図2 データ・コンバータの高速シリアル・インターフェイス

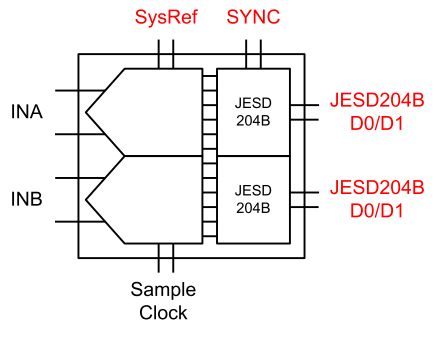

JESD204B対応のシリアルA/Dコンバータの例。内蔵のJESD204B回路でシリアル-バラレル変換を行い、FPGAなどとシリアル接続できる。

今回は、JESD204の概要と、その最新バージョンであるJESD204Bに対応した業界最高速の2チャネル16ビットA/Dコンバータ、業界初のクロック・ジッタ・クリーナを紹介する。

高速A/Dコンバータ、D/Aコンバータの課題を解決するJESD204

JESD204は、A/Dコンバータ、D/Aコンバータのためのシリアル・インターフェイスの規格として、2006年に最初に策定された。これは、コンバータとFPGAなどのロジック・デバイスを接続するシリアル・インターフェイスであり、電気的特性、データストリーム(トランスポート層、データリンク層)、トランスミッタ動作、レシーバ動作などが規定されている。

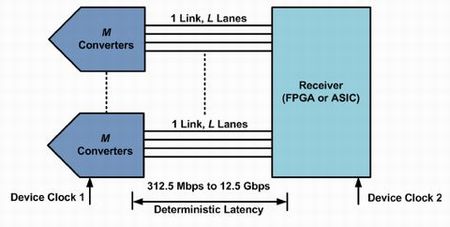

当初の規格は、コンバータとロジック・デバイスを1対1で接続するものであり、1レーン、1リンクで312.5Mbpsから3.125Gbpsまでの信号レートが規定されていた(図3)。

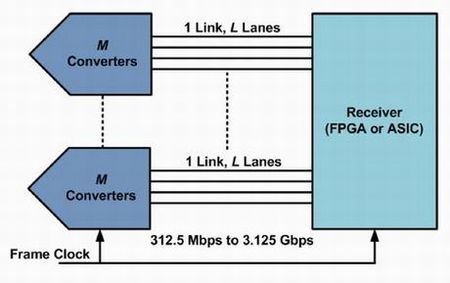

JEDECでは引き続きJESD204の拡張を進め、2008年にはレーンの並列化と、複数コンバータの接続をサポートするJESD204Aを策定した。

JESD204Aでは、同期して動作するL本のレーンを用いることによって、実質的な信号レートをL倍に向上できる。逆に、1レーンあたりの信号レートを下げてノイズ低減やコストダウンを図ることも可能になった。

また、JESD204Aでは、1台のデバイスに接続した複数のコンバータの動作もサポートされるようになった(図4)。

2011年には、さらに大きな拡張を加えた最新バージョンのJESD204Bが策定された。

JESD204Bでは、まず1レーン、1リンクでの信号レートが最大12.5Gbpsと、従来の4倍に高速化された。これによって、例えば250Msps、16ビットという高速・高分解能のコンバータが1レーンで実現可能になった。

また、JESD204Bでは、サンプリング・タイミングからデジタル・データ出力までの遅延時間を一定に管理できるdeterministic delayの機能が追加された。コンバータとロジック・デバイスの同期も、従来のフレーム・クロックに加えて、より柔軟に利用できるデバイス・クロックがサポートされた。

なお、JESD204Bではサポートする機能によって、サブクラス0、サブクラス1、サブクラス2という三つのサブクラスが定義されている(図5)。

図5 JESD204Bへの拡張(2011年)

現行版のJESD204Bでは、1レーンあたりの信号レートが12.5Gbpsに高速化され、定遅延(Deterministic Delay)やデバイス・クロックのサポートが追加された。

JESD204、JESD204A、JESD204Bの比較を表1に示す。

| 発表 | 最大信号レート | マルチレーン | レーン間同期 | サブクラス | |

|---|---|---|---|---|---|

| JESD204 | 2006年 | 3.125Gbps/レーン | なし | なし | |

| JESD204A | 2008年 | 3.125Gbps/レーン | あり | あり | |

| JESD204B | 2011年 | 12.5Gbps/レーン | あり | あり | 0 定遅延サポートなし(後方互換用) 1 SYSREFによる定遅延サポート 2 SYNCによる定遅延サポート |

表1 JESD204、JESD204A、JESD204Bの比較

JESD204によって、高速データ・コンバータの配線が大幅に削減され、ボード面積やシステム・コストの低減が可能になった。特に、最新バージョンのJESD204Bでは、十分な高速性と使いやすい同期機能をサポートしており、今後の高速データ・コンバータはJESD204B対応が主流になっていくと考えられる。

FPGAメーカでもJESD204B対応のI/O機能のサポートを早くから進めており、インターフェイスとして利用可能になっている。

JESD204B対応、業界最高速の2チャネル16ビットA/Dコンバータ ADS42JB69

テキサス・インスツルメンツ(TI)のADS42JB69は、JESD204Bに対応し、2チャネル16ビットA/Dコンバータとして業界最高速の250Mspsを実現した。単に高速化、シリアル化しただけでなく、SNRやSFDRなどのダイナミック特性もきわめて優れた特徴をもつ。また、消費電力も775mW/チャネルときわめて低く抑えられている。無線基地局をはじめ、超音波診断装置などの医療機器、計測/テスト機器などのアプリケーションで注目されている。

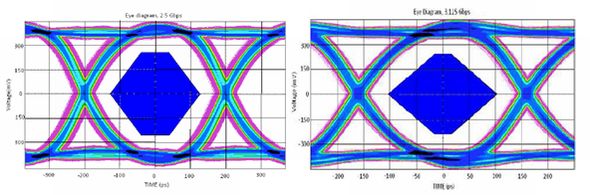

ADS42JB69は、JESD204Bのサブクラス0〜2のすべてに対応し、deterministic delay(定遅延)をサポートしているので、アプリケーションのさまざまな仕様に柔軟に利用できる。最大3.125Gbpsのシリアル・インターフェイスを4レーン持ち、2チャネル16ビットで250Msps動作に必要なデータレートを実現できる(図6)。

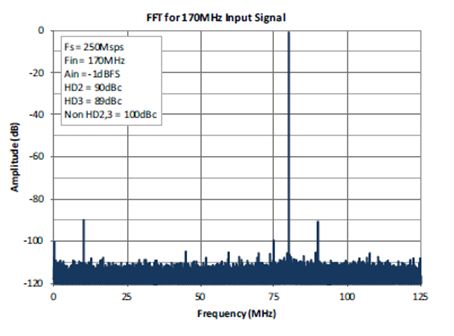

また、fin=170MHzにおいて、フルスケール基準で最大74.9dBのSNR、最大89dBcのSFDRなど、A/Dコンバータとしてのダイナミック特性でも、業界最高を実現している。それによって、無線レシーバの受信感度を大幅に向上できる(図7)。

図7 fin=170MHzにおけるSFDR

fin=170MHzにおけるFFTの図を示す。第2高調波(340MHz)で90dBC、第3高調波(510MHz)で89dBC、それ以外の周波数では100dBCのSFDRが得られている。

図8 ADS42JB69EVM、JESD204B-パラレルLVDS変換ボード、TSW1400EVMの接続例

ADS42JB69の評価用モジュールとJESD204B-パラレルLVDS変換ボードが用意されており、既存のデータ・キャプチャ/パターン生成プラットフォームに接続して評価・開発ができる。

さらに、TIではADS42JB69を用いた回路設計を迅速に実現するための評価用モジュールもすでに供給を行っている。

ADS42JB69の評価用モジュールであるADS42JB69EVMと、FPGA搭載のJESD204B-パラレルLVDS変換ボードが用意されており、従来から用いられているコンバータ評価用の高速データ・キャプチャ/パターン生成プラットフォームTSW1400EVMに接続できる。ADS42JB69EVMとJESD204B-パラレルLVDS変換ボードを組み合わせたADS42JB69SEKは、参考価格999ドルで供給中という。また、Xilinx社やAltera社のFPGA開発プラットフォームにも接続可能である(図8)。

ADS42JB69はJESD204B対応のシリアルA/Dコンバータだが、TIでは、これと同等のA/D変換性能をもち、パラレルLVDSインターフェイスを装備したA/Dコンバータとして、ADS42LB69を製品化している。さらに、ADS42JB69とピン互換の14ビット版としてADS42JB49、ADS42LB69とピン互換の14ビット版としてADS42LB49を発売している。

JESD204B対応、業界最高性能の高速クロック・ジッタ・クリーナLMK04828

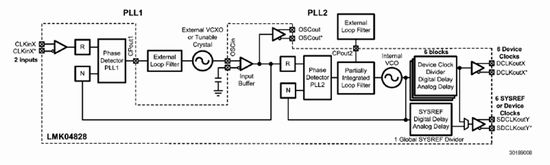

TIでは、JESD204B対応の高速A/DコンバータであるADS42JB69と合わせて、きわめて低ジッタのクロックとJESD204Bサブクラス1のSYSREF信号をペアで供給可能な業界初のクロック・ジッタ・クリーナLMK04828を製品化している(図9)。

図9 LKM04828のブロック図

LMK04828はJESD204対応の低ジッタ、高機能クロック・ジェネレータ。外付けVCXO(PLL1)と内蔵VCXO(PLL2)を用いてデュアルPLLを構成した例を示す。

LKM04828は、内蔵の低ノイズVCXOモジュールを用いて、245.76MHz出力時に100fsRMS未満という低ジッタ(10kHz〜20MHz)のデバイス・クロックを7チャネル供給できる。また、各デバイス・クロックにSYSREF信号をペアで供給可能であり、SYSREF信号を用いない場合は最大14チャネルのデバイス・クロックとして供給することもできる。また、各出力はLVPECL、LVDS、HSDSに設定でき、デジタル遅延、アナログ遅延、ゼロ遅延などのクロック機能をサポートする。

ADS42JB69と組み合わせることにより、最高のシステム性能を得るとともに、部品点数やコストの大幅な削減が可能になる。評価用モジュールであるADS42JB69EVMでは、ADS42JB69とLKM04828を組み合わせて搭載している。

JESD204B データ・コンバータ・インターフェイス 概要ビデオ(日本語字幕付き)

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.