フィールド プログラマブル デバイスによる最適解、さらにコスト削減も:あのASICが供給中止!? 代替ソリューションをお探しのあなたに朗報!

世界にひとつしかないASICが供給中止になったら……。ASICの代替を時間をかけずに実現するのが「フィールド プログラマブル デバイス」だ。中でもアナログ混載や小規模ロジックには、サイプレスの「PSoC」が最適解となるだろう。

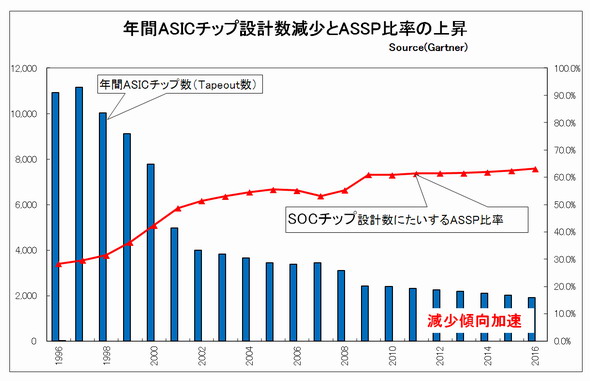

最近、新聞紙上やWebメディアを賑わしている記事のひとつに「日本の半導体ベンダの事業方針変更」がある。システムLSI事業の不採算が続く中で、事業の縮小やフォーカス分野の変更が相次いで発表されているのだ。システムの差別化のキーデバイスであったASIC事業もご多分に漏れず、サプライヤからの供給中止の通知がシステムベンダの多数の担当者に送られているのが現状だ(図1)。

個々のASIC(品種)は世界にひとつしかないわけだから、その供給中止は致命的で、代替品を探す作業が急務となっている。時間をかけて探すわけにもいかない状況下では、早急に実現できる「フィールド プログラマブル デバイス」がその代替解となる。大規模なロジックではFPGAかもしれないが、アナログ混載や小規模ロジックにはサイプレスのPSoC®(Programmable System on Chip)が現在入手できる“最適解”の製品となるだろう。本稿では、後者のPSoCがいかに最適な代替ソリューションであるかを、実際例を交えて紹介する。

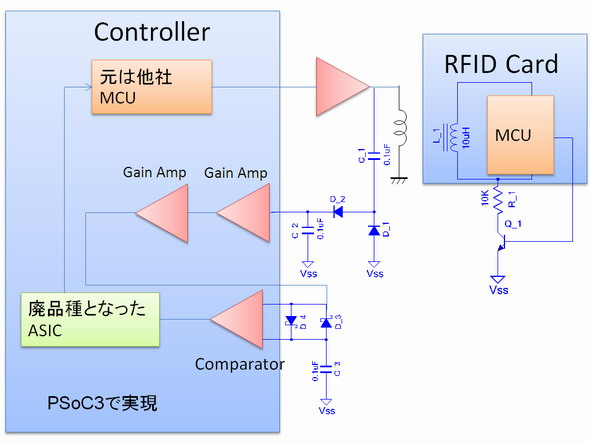

図2は、昨年(2012年)実際に起こった例で、ASICをPSoCで代替している。黄緑色の部品が供給中止を通知されたASICだ。これをシステムベンダが、周辺に残っていたアナログ部品とMCUとを集積してPSoC 3にまとめた。どんなソリューションでもじっくりと時間をかければできることだが、短期間にプロトタイプを作って検証できるのはフィールド プログラマブル デバイスの大きな利点だ。日本でのこうしたソリューションの普及に努めてこられた熊本大学の末吉敏則教授が提唱する「やわらかいハードウェア」でなければできないことだ。この例では実際には2カ月ほどでPSoCによる機能実現を検証できている。

PSoCはこうしたASICの供給中止の代替デバイスとしてだけでなく、集積化から取り残されたアナログ個別半導体(例:オペアンプ、AD変換素子)の集積化によるコストの削減や、5V供給の古いFPGAの供給中止における代替品としても使用できる。

サイプレスのPSoCは、組み込みシステム市場におけるデジタルとアナログ混載の集積化のためのプラットフォームと位置付けられている。チップの中にMCUコア(8bitの8051系やARM Cortex)が搭載されているが、PSoCの価値はチップ上のデジタルおよびアナログのリソースであり、それがフィールド プログラマブルであり、そしてそれをデスクトップPCで設計可能な点である。

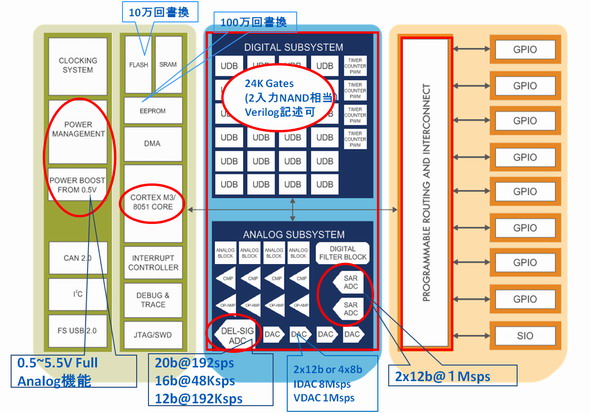

PSoCのリソースを図3に示す。デジタル部はCPLD(入力の積和演算)とALUを含むデータパスからなり、CPLDでいう512マクロセルの搭載が可能だ。配線および入出力I/OはFPGAとほぼ同様にAny pin、Any location(デジタル、アナログの区別なく)の割り当てが可能となっている。

アナログ部はPSoCの最もユニークな部分だ。高速あるいは高精度のAD変換回路は専用回路となっており、12bit 1Mspsの逐次近似型AD変換そして8~20bitのデルタシグマAD変換回路がある。後者の分解能、そして指数的に反比例するサンプリング スピードは可変(プログラマブル)設定できる。それ以外のアナログ リソースは基本的にはスイッチト キャパシタと連続タイミング ブロックの基本素子からなり、それを組み合わせることによってゲイン値や抵抗値を変えられるオペアンプ、ペアゲインアンプ、電流→電圧変換、アナログマルチプレクサなどが組める。

最後にPSoCの設計環境を紹介しよう。専用のPSoC Creator™は無償でサイプレスのWebからダウンロードが可能でPCで使用できる。アナログ部の設計には内蔵された回路図エディタを使用する。分解能やゲイン値の設定も、優れたGUIにより簡単に行える。また、一部の回路素子からはSpiceネットリストが生成できる。一方デジタル部は、ユーザーマクロの中にVerilog-HDLコード記述を入れると、内蔵された論理合成ツールと静的タイミングツールにより検証合成ができる。これらをトップレベルで結合し、コンパイルすれば回路全体のCコードが作られ、必要によりシステム制御のためのCコードを加えることができる。全ての回路素子内の結線情報はCコード上ではファンクション コールの形でCコード上に現れる。これをコンパイルしてHEXに変換したものをチップのフラッシュメモリに書き込む。これが開発の一連の流れとなる。

PSoCは、ユーザーアプリケーションに必要な種々の機能を、フレキシブルに、簡単に、かつ短期間で統合するこが可能で、ASICなどの供給中止に直面した場合の代替策として容易に使用することが可能だ。サイプレスではその設計手法の基本を習得するためのワークショップ(参加無償)の開催も実施している。製品およびワークショップの詳細は下記を参照いただきたい。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本サイプレス株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年4月13日