IBISモデル

IBISモデルとは、プリント基板上の配線ラインを流れる信号波形を解析する伝送線路シミュレーションに向けたICの解析モデルのこと。「Input/Output Buffer Information Specification」の頭文字をとって、IBISモデルと呼ばれる。現在、ICの解析モデルとして広く普及しており、SPICEモデルとともに業界標準になっている。

インテル主導で開発される

IBISモデルが登場したのは1993年のことだ。IBIS Open Forumによって策定された。その当時、SPICEモデルは既に実用化されていた。それなのに、なぜIBISモデルを開発する必要があったのか。それは、SPICEモデルはトランジスタ・レベルで記述されており、そのICの製造に必要な半導体プロセスの詳細情報を記載しなければならなかったからだ。具体的には酸化膜の厚さなどである。半導体メーカーにとって、こうした情報は極めて重要である。競合する半導体メーカーには漏らしたくない。このため半導体メーカーは、電子機器メーカーとの間で秘密保持契約などを結び、提供していた。

しかし、これでは電子機器メーカーにとって入手性が悪い。しかも当時、パソコンの高性能化が急ピッチに進み、配線ラインの伝送線路シミュレーションが不可欠になりつつあった。SPICEモデルを入手できなければ、シミュレーションを実行できない。つまり、パソコンを設計できない。

そこでマイクロプロセッサ大手のインテルが主導して組織されたのがIBIS Open Forumである。この団体において、半導体プロセスの詳細情報が外部に漏れない、新しいICの解析モデルの開発が始まった。

度重なる改訂で精度を高める

トランジスタ・レベルのSPICEモデル。一方、IBISモデルでは、ICの中身をブラック・ボックス化し、その動作を記述する手法を採用した。いわゆるビヘイビア・モデルである。

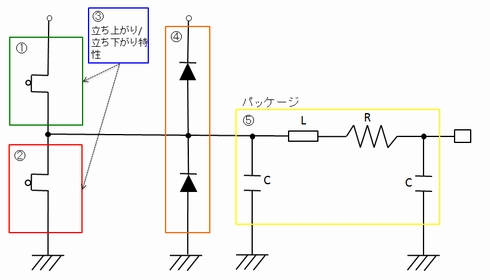

当初のIBISモデルは、5つの要素から構成されていた(図1)。1つはハイ(高)レベルのドライバの電圧・電流特性、2つ目はロー(低)レベルのドライバの電圧・電流特性、3つ目はそれらの立ち上がり/立ち下がり特性、4つ目は、電源あるいはグラウンドとの間のダイオード、5つ目はパッケージの抵抗(R)、インダクタンス(L)、静電容量(C)である。

IBISモデルでは、製造プロセスの詳細情報は一切必要ない。このため、パソコン業界を中心に、広く普及していった。しかし、半導体技術やマイクロプロセッサ技術の進化とともに、IBISモデルに次第にほころびが見え始めてきた。「シミュレーション結果と実測結果が合わないという精度の問題」である。

そこでIBIS Open Forumでは度重なる改訂を行い、バージョンアップを実行することで精度の問題に対処してきた。例えば、バージョン2.1(IBIS v2.1)では、ECLやPECL、差動形式の入出力インタフェイスに対応した他、波形テーブル機能を追加した。バージョン3.0(IBIS v3.0)では、ドライバの選択機能、エレクトリカル・ボード記述(EBD)機能、マルチステージ・ドライバ機能などを新たに盛り込んだ。

図1 IBISモデルの基本構成

IBISモデルが開発された当初の基本構成である。5つの要素から構成されている。1つはハイ(高)レベルのドライバの電圧・電流特性、2つ目はロー(低)レベルのドライバの電圧・電流特性、3つ目はそれらの立ち上がり/立ち下がり特性、4つ目は、電源あるいはグラウンドとの間のダイオード、5つ目はパッケージの抵抗(R)、インダクタンス(L)、静電容量(C)である。

IBIS-AMIが登場

最近では、バージョン5.0(IBIS v5.0)において、高速なSerDes(シリアライザ/デシリアライザ)回路のシミュレーションに向けた新しいモデル・フォーマットである「IBIS-AMI(IBIS-Algorithmic Modeling Interface)」が追加された。このモデルを使えば、高速なSerDes回路の伝送線路シミュレーションを高い精度を確保しつつ、短時間に実行することが可能になる。

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2015年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.