コンバーターの回路方式:DC-DCコンバーター活用講座(4) 電力安定化(4)(3/3 ページ)

今回の記事では、同期式と非同期式の違いの他、2段式やマルチフェーズといったコンバーターの回路方式について説明する。

マルチフェーズDC-DCコンバーター

マルチフェーズDC-DCコンバーターは、エレクトロニクスにおける平衡原則の良い例です。つまり、恩恵を得るには、それに釣り合う何らかの不利益の対価を支払う必要があります。処理能力向上のためのスイッチング速度の高速化の追及により、代表的マイクロプロセッサのコアの電圧は5Vから3.3Vへ、さらに1V以下へと低下し、他方ゲートの複雑さが増すにつれてますます高い電源電流が求められています。

とはいえ、低電圧かつ高電流の電源を作るのは容易ではありません。

マルチフェーズDC-DCコンバーターの需要が増加しているのは、部分的には出力フィルター部品の制限のためです。高い負荷電流で出力リップルを必要なレベルまで下げるためにフィルターの値を任意に大きくすることは、技術的理由と経済的理由の両方により不可能です。

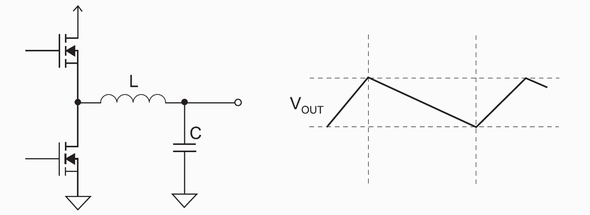

さらに、ますます小さなフォームファクタが要求されるので、出力のインダクターとコンデンサーを物理的にそれほど大きくできません。そのため、新しいテクノロジーが必要です。マルチフェーズテクノロジーの長所を示すため、まずシングルフェーズの形式を先に示します。

反復する充放電サイクルの間、出力電圧はリップルVRIPPLEのピーク-ピークの大きさだけ変化します。負荷電流が増加すると、放電電流が増加し、充電電流が自動的に増加します。つまり、FET、インダクタンスLおよびコンデンサーCを通って電流が増加します。VRIPPLEを小さく保つには、スイッチング周波数とLおよびCの値を増やす必要があります。

しかし、効率を高く保つには、FET、インダクターおよびコンデンサーの直列抵抗値を低くしなければばらないので部品サイズが大きくなり、またEMCが懸念されるので最大周波数が制限されます。

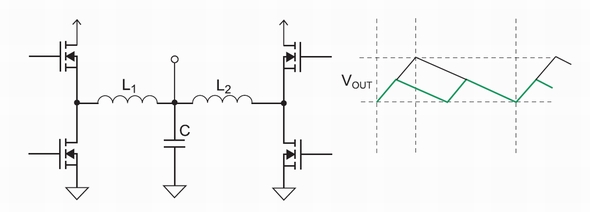

マルチフェーズコンバーターは、いくつかの部品の間で負荷電流を分担することにより、この難題を解決します。2フェーズ構成の原理を図7に示します。

マルチフェーズ出力の短所の1つは、追加されるフェーズ毎に2個の追加FETと1個のインダクターが必要になるため、部品コストが高くなることです。また、フェーズをずらした複数の出力を発生するように制御ICを設計する必要があります。

しかし、前に述べたように、インダクタンス値を小さくすることができるので、デザインがはるかに小さくなります。コンデンサーの値も小さくすることができます。位相をずらして個々の出力をオンすれば、結合された出力電圧の最大振幅が減少し、電流がもっと均一になり、従ってEMIが減少します。

つまり、入口でのフィルタリングの量も小さくすることができます。さらに、出力コンデンサーを小さくすることができるので、負荷の変化に対する応答時間が加速され、セトリング時間が短縮されます。

2フェーズ出力は一般に180度ずらします。3フェーズ出力は120度にします。ただし、4フェーズ出力は通常逆位相で動作する2組のペアに構成します。その理由は、回路を流れる位相のずれた反射入力電流が多すぎない方が、パルス入力のEMCフィルタリングの設計が簡単だからです。

降圧、昇圧またはSEPICの構成にすることができ、短絡保護および入力の低電圧ロックアウト回路を内蔵した、組み合わせて使えるマルチフェーズコントローラーICが市販されています。

⇒「DC-DCコンバーター活用講座」連載バックナンバーはこちら

(次の記事を読む)

※本連載は、RECOMが発行した「DC/DC知識の本 ユーザーのための実用的ヒント」(2014年)を転載しています。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

インターリーブのススメ、昇圧型スイッチング・レギュレータを高効率に

インターリーブのススメ、昇圧型スイッチング・レギュレータを高効率に

マルチフェーズのインターリーブは単相よりも設計は複雑だが、発熱や基板面積、さらにはコストをも抑えられる。 最大効率94%の同期整流式降圧レギュレーター

最大効率94%の同期整流式降圧レギュレーター

アナログ・デバイセズは、最大効率94%(2MHz時)の同期整流式降圧スイッチングレギュレーター「LT8645S」を発売した。1チップにパワースイッチ、昇圧ダイオード、発振器、制御回路、ロジック回路などを集積している。 POL向け12V同期整流降圧レギュレーター

POL向け12V同期整流降圧レギュレーター

ルネサスエレクトロニクスの子会社であるインターシルは、POL向けの12V同期整流降圧レギュレーター「ISL850xx」ファミリーに、出力電流14A、12A、9A、5Aタイプを追加した。出力電圧は最小0.6V、入力電圧は3.8〜18Vとなっている。 漏れインダクタンスを使用したフライバックコンバーター(1)ハードウェア概要

漏れインダクタンスを使用したフライバックコンバーター(1)ハードウェア概要

電圧モード(VM)で動作し、連続導通モード(CCM)で駆動されるフライバックコンバーターの周波数応答は、2次システムの応答に相当します。解析結果の大部分から、伝達関数の品質係数が各種損失(経路の抵抗成分、磁気損失、リカバリー時間に関連する損失など)によってのみ影響を受けることが予測される場合、漏れインダクタンスに起因する減衰効果がもたらす影響は非常に限定的です。ただし、過渡シミュレーションでは、漏れインダクタンスが増大すると出力発振が減衰することが予測されます。文献に記載されている多くの式はこの効果を反映していないので、新しいモデルが必要となりますが、本稿はこのモデルについて説明します。 同期整流器の動作タイミングを制御する回路

同期整流器の動作タイミングを制御する回路

同期整流器を採用する際に問題になるのは、スイッチングのタイミング制御が複雑になることだ。本稿では、この動作タイミングを制御する回路を紹介する。![DC-DCコンバータのノイズ対策[理論編]](https://image.itmedia.co.jp/edn/articles/0812/01/news136.gif) DC-DCコンバータのノイズ対策[理論編]

DC-DCコンバータのノイズ対策[理論編]

スイッチング方式のDC-DCコンバータは、その仕組みから、ノイズの発生源となってしまう可能性がある。これを避けるために、設計者は適切な対処法を知っておかなければならない。本企画では、2回にわたり非絶縁型/スイッチング方式のDC-DCコンバータのノイズ対策について実践的に説明する。今回は『理論編』として、ノイズの種類やノイズの発生メカニズムを中心に解説を行う。