開ループと閉ループの設計:DC-DCコンバーター活用講座(12) 帰還ループ(1)(2/2 ページ)

今回から、帰還ループ補償の計算とその方法について取り上げます。今回の記事では、開ループと閉ループの設計について解説します。

閉ループの設計

帰還ループを使用することで、出力が入力電圧に依存しないようにすることができます。基本的に、帰還経路はエラーアンプに接続されます。エラーアンプは実際の出力と望みの出力を比較し、出力を補正して一致させます。補正は常に誤差と反対方向に行われる(出力が高すぎれば下げ、出力が低すぎれば上げる)ので、この帰還は「負」と呼ばれます。帰還ループが「正」の場合、あらゆる誤差が増幅され、出力は発振するか、あるいは、急激に最小または最大レベルになります。過渡動作状態で正の帰還条件が発生しないようにすることが、ループ設計の最も難しい課題の一つです。

帰還の長所は、負荷の変化による出力電圧の変化だけでなく、入力電圧の変化も補償されることです。同じ帰還ループで両方の状況を補正することができます。閉帰還ループの別の長所して、入力と出力の構成が同じである必要がないことが挙げられます。帰還ループを使用して、可変入力電圧電源から定電流を生成することができます。エラーアンプは出力電圧ではなく、単純に出力電流に基づいた帰還信号に応じて、出力を調整します(実際には、電圧アンプではなく、トランスコンダクタンスアンプになります)。

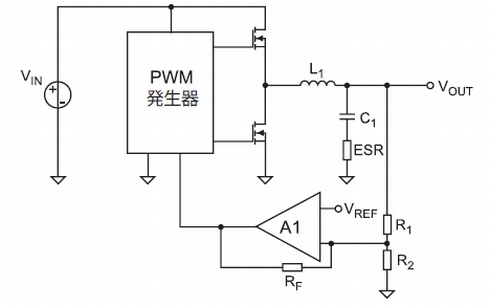

簡単な非絶縁型降圧レギュレーターを使って、帰還設計を分析しましょう。標準的な回路図は次のようになります。

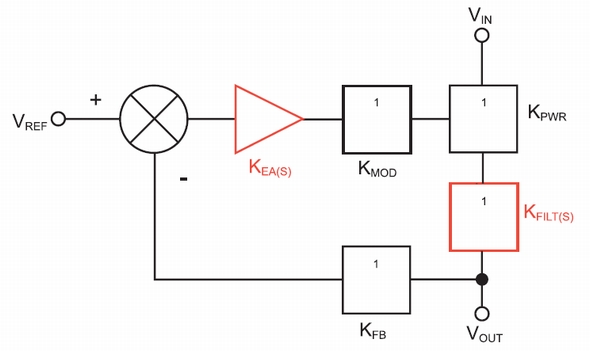

機能ブロックの観点からみると、図2.1は以下のようになります。

機能ブロックごとにゲインKがあります。パワースイッチング素子(FET)のゲインはKPWR、L1とC1で形成された出力フィルターのゲインはKFILT(S)、帰還素子(R1と R2で形成された抵抗分圧器)のゲインはKFBです。結果として生じる帰還信号は加算点で基準電圧VREFと比較され、ゲインがKEA(S)のエラーアンプA1によって誤差が増幅されて、ゲインがKMODのPWM変調器を制御します。これらのゲインブロックには、増幅度が高いものもあれば、信号を減衰するものもありますが、全体の開ループゲイン(全てのゲインの合計)は正になり、通常およそ1000です。

図1に示した簡単な回路は、出力LCフィルターに起因する、次式に示す周波数の共振点(ポール)を持ちます。

さらに、コンデンサーのESRに起因するもう一つの共振点(ゼロ)を持ちます。

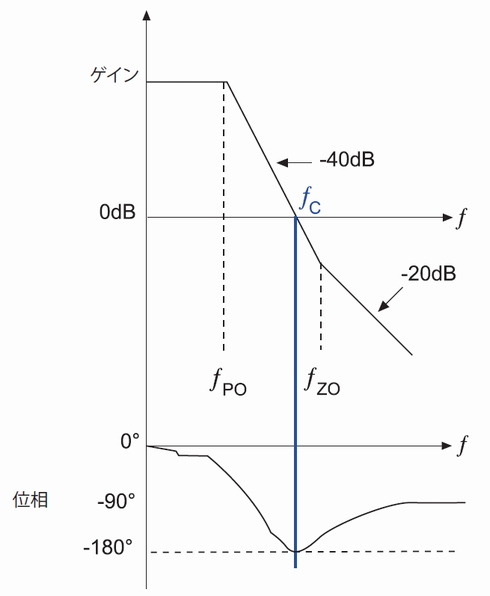

fPOより高い周波数では、出力フィルターの2次LC特性により、ゲインが−40dB/decadeのレートで減少します。ゲインがユニティ(ゲイン=0dB)に達するポイントがクロスオーバー周波数fCです。周波数fZOで、フィルターコンデンサーのESRに起因する1次RCフィルターの影響により、ゲインのスロープが−20dB/decadeに変わります。周波数に対する正規化ゲインをプロットすると、スロープと位相が周波数と共に変化することが分かります。

位相プロットは、エラーアンプA1での入力周波数の反転による180°が付加された位相変化です。

この位相プロットから分かるように、クロスオーバー周波数での位相変化が合計で−180°または−360°なので、この回路はクロスオーバー周波数で不安定になります。このため、コンバーターが正帰還領域に入り、出力がリンギングを開始するか、急に発振状態になります。

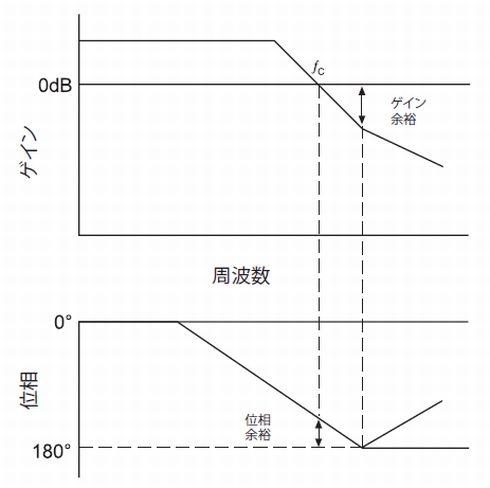

エラーアンプ段のゲインを増加させることにより、全体のゲインがユニティになる周波数をより安全な領域に移動させることができます。位相余裕(システムのfCにおける全体の位相と−180°との差)とゲイン余裕(位相が−180°のときのシステムのゲイン)により、帰還ループがどれだけ安定しているかが決まります(図4)。

⇒「DC-DCコンバーター活用講座」連載バックナンバーはこちら

(次の記事を読む)

※本連載は、RECOMが発行した「DC/DC知識の本 ユーザーのための実用的ヒント」(2014年)を転載しています。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

![DC-DCコンバータのノイズ対策[理論編]](https://image.itmedia.co.jp/edn/articles/0812/01/news136.gif) DC-DCコンバータのノイズ対策[理論編]

DC-DCコンバータのノイズ対策[理論編]

スイッチング方式のDC-DCコンバータは、その仕組みから、ノイズの発生源となってしまう可能性がある。これを避けるために、設計者は適切な対処法を知っておかなければならない。本企画では、2回にわたり非絶縁型/スイッチング方式のDC-DCコンバータのノイズ対策について実践的に説明する。今回は『理論編』として、ノイズの種類やノイズの発生メカニズムを中心に解説を行う。 電流モード制御DC-DCコンバータの特性改善

電流モード制御DC-DCコンバータの特性改善

電流モード制御のDC-DCコンバータは、どの位置で電流検出を行うかによって特性が大きく左右される。本稿では、従来の設計の問題点を指摘するとともに、DC-DCコンバータの種類ごとに電流検出の最適な位置について解説する。 サレンキー型フィルタの“落とし穴”

サレンキー型フィルタの“落とし穴”

サレンキー(Sallen-Key)型のローパスフィルタは、遮断周波数以上の領域では、フィルタのゲインが単調に減衰しないという落とし穴がある。一定の周波数を超えると、周波数の増加とともにゲインも増加してしまうのだ。 「アイソレータ」を活用せよ!

「アイソレータ」を活用せよ!

絶縁技術を利用することで、機器の安全性を保証したり、ノイズを低減したりすることが可能になる。絶縁を実現するにはアイソレータを適切に選択しなければならないが、それには各種アイソレータがそれぞれどのような手法で実現されているのか、その特性はどのくらいのものなのかといったことを理解しておく必要がある。 スルーレート制御で電源のEMIを減らす

スルーレート制御で電源のEMIを減らす

オフラインのスイッチング電源が放射する電磁雑音(EMI)は電源回路全体に影響を与えるため、さまざまな問題が発生する。基板レイアウトは特に重要だ。今回は、電圧と電流のスルーレートを閉ループ回路で制御することで雑音を低減する回路を紹介する。 電流帰還型オペアンプのメリット

電流帰還型オペアンプのメリット

「電流帰還型」という言葉からは、あるいは何か特別なものであるかのような印象を受けるかもしれない。しかし、いずれの方式であっても、それを使ったオペアンプ回路としての基本的な構成には違いはない。ただし、回路構成以外の部分では、いくつかの重要な違いがある。