複雑化するFPGAパワーシステムに向けた最新パワーシステムマネージメントデバイス(DPSM):アナログ回路設計講座(39)

FPGAはあらゆるタイプの電子機器へ浸透し、ASICにとって代わりつつあるが、それを取り巻くパワーシステムは複雑になっています。複雑になりつつあるFPGAパワーシステムをどのように管理すればよいか。最新のFPGAパワーシステム用マネージメントデバイスを例に挙げながら考察していこう。

フィールド・プログラマブル・ゲート・アレイ(FPGA)の起源は1980年代にまでさかのぼり、元々はプログラマブル・ロジック・デバイス(PLD)から発展したものです。それ以降、FPGAのリソース、速度、効率は急速に向上し、幅広い計算および処理アプリケーションの要となるソリューションとなりました。特に、生産量がASIC(特定用途向け集積回路)の開発コストに見合わない場合に多用されてきました。今日、FPGAは家電にも搭載されるほど量産展開されるようになりました。例えばMicrosoftは、2013年のパイロットプログラムでFPGAを使用したBing検索エンジンの速度向上に成功した後、クラウドデータセンターでもFPGA搭載のサーバを使用するようになりました。

FPGAパワーシステムの条件

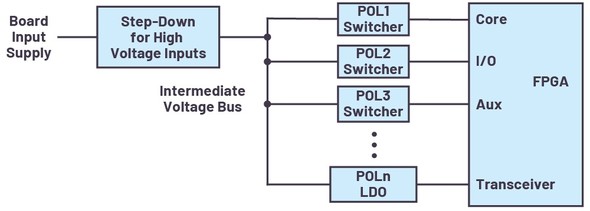

FPGAには、その内部コアロジック、I/O回路、補助ロジック、トランシーバー、メモリに電力を供給するために、異なる電圧および、電流仕様を持つ複数の低電圧電源レールが必要です。通常、これらのレールは、FPGAの損傷を避けるために固有のシーケンスでオン/オフする必要があります。ポイント・オブ・ロード(POL)レギュレータは、ボードの高い入力電源電圧を、FPGAが必要とする複数の低いレール電圧に降圧します。電力変換効率が重視される場合はスイッチングレギュレータがPOLレギュレータとして使われますが、PLLやトランシーバーなどのノイズに敏感な回路にはリニアレギュレータ(例えば低ドロップアウト[=LDO]レギュレータ)が使われます。

代表的なボード入力電圧は5V、12V、24V、48Vで、FPGAのレール電圧は1V未満から約3Vの範囲です。入力電圧が高い(12V、24V、48V)場合は、POLレギュレータへの給電に使用する中間電圧バスを生成するために、追加で降圧が必要となることがあります(図1参照)。これらのFPGAレールの中で最も低い電圧(約1Vまたは1V未満)と最も高い精度(±3%以上)を必要とするのがコア電源で、電流レベルはFPGAリソースの使用状況に応じて数十アンペアになります。ロジックエラーを防ぐには、DC条件下だけに限らずFPGAの電流トランジェント時においても、FPGAのレール許容差仕様に従って電源の変動を数十ミリボルトの範囲に制限する必要があります。電源のDC精度が低下するほど、トランジェント条件下で受け入れ得る電源電圧を維持するために、容量の大きいバイパスコンデンサが必要になります。例えば、コア電圧の許容差仕様が±3%と想定します。精度が±1%のDC電源を使用した場合、トランジェントに対する許容差は±2%になります。これに対し、より精度の低い±2%のDC電源を使用すると、トランジェントに残された余裕は少なくなり(±1%)、上述の場合よりも大きな容量のバイパスコンデンサが必要になります。

最終局面での設計変更や別のアプリケーションへの設計の再利用、ボードマージンテストなどを行ったり、開発段階や現場運用時にシステムの消費電力を動的に最適化したりする場合、FPGAの電源電圧レベルをデフォルト設定点付近にトリミングする必要があります。このような状況で最も迅速な解決策、あるいは最も実現しやすい解決策は、電源の帰還回路に異なる抵抗をハンダ処理することではありません。電圧トリミングを実現する方法の1つは、D/Aコンバータ(DAC)を使用して電圧レギュレータの帰還回路を駆動することです(図2参照)。この場合、A/Dコンバータ(ADC)から電源電圧測定データを取得し、正しいDACコードを計算し、さらにDAC出力をゆっくりと調整して計算コードに合わせ、グリッチやオーバーシュートを生じさせることなく電源電圧を目標レベルまでスムーズに上昇させる、というトリムルーチン用のソフトウェアコードを書き込む必要があります。このトリムルーチンは時間の経過に合わせて繰り返し、時間や温度と共に部品に生じるドリフトによって電源が目標電圧から外れないようにする必要があります。

FPGAは電子システムの頭脳となる部分なので、さまざまな状況下でのシステムの状態と消費電力を把握するには、FPGAの電源電圧、電流および、故障を監視することが不可欠です。このような状態の理解とトリミング機能を組み合わせれば、最も厳しい条件での電源設計を行う必要がなくなり、コストと電力を節約することができます。さらに、将来的に予測される不具合をFPGA消費電力の異常傾向として顕在化させ、ボードやシステムがダウンする前にホストコントローラやサービススタッフに警告を発することができます。電圧モニタリングにはADCが必要であり、電流モニタリングにも、ハイサイド電流検出電圧をグラウンド基準の電圧に変換するためのレベルシフト回路が必要です(例えば図3に示すトランスコンダクタンスアンプ)。

障害管理についてはまだ検討していませんが、これまでのさまざまな条件を考慮するだけでも大変なことです。POL出力が低電圧または過電圧の状態になった場合、つまり有効な電圧ウィンドウを外れた場合には、どのようなことが起こるのでしょうか? 不具合が生じた電源だけをオフにすれば良いのでしょうか。あるいは他の電源もオフにすべきでしょうか。そして、ボードをシャットダウンさせた障害から回復、解決するには、どうすれば良いのでしょうか。

FPGAのパワーシステム管理はすぐに複雑なものとなってしまう可能性があり、肝心のFPGAアプリケーションから焦点がそれてしまいがちだということは容易に想像できると思います。FPGAのパワーツリーは、デジタル処理ボード上の全体的なパワーシステムの一部にすぎません。以上に挙げた条件のほとんどは、ASIC、DSP、GPU、SoC、マイクロプロセッサといった他のデジタルデバイスにも当てはまります。必要なのは、シンプルでスケーラブル、なおかつ柔軟なパワーシステムマネージメントソリューションです。

デジタルパワーシステムマネージメント

アナログ・デバイセズは、デジタル処理ボードに見られる複雑なパワーシステムを扱う、デジタルパワーシステムマネージメント(DPSM)デバイスのポートフォリオを提供しています。DPSMデバイスにはDC/DC変換機能を内蔵したものとそうでないものがあり、これらはPOLレギュレータの代わりに使用するか、既存のPOLレギュレータと共に使用します。パワーシステムマネージャ(DC/DC変換を行わないもの)は既存のアナログパワーシステムにデジタルモニタリング機能と制御機能を加えたもので、複数のスイッチャまたはLDOレギュレータで構成されています。LTC2980などのデバイスは、1つで16個のPOLレギュレータのトリミング、マージニング、モニタ、シーケンシング、監視、障害ログ作成、および障害管理を行います。チャンネル数の異なるデバイス(2、4、8、または16チャンネル)を組み合わせて、数百個のレールを管理することが可能です。2チャンネルのLTC2972はこのポートフォリオに加わった最新の製品で、例えばFPGAコアや補助レールなどのパワーシステムにおける2つの最重要レールのモニタリングと制御用に、シンプルで導入的なソリューションを提供します。

2チャンネルパワーシステムマネージャ

LTC2972は2チャンネルのパワーシステムマネージャで、FPGA、ASIC、プロセッサなどを使用したボードにソフトウェアベースの包括的なモニタリング機能、制御機能、ブラックボックス障害記録機能を追加したものです。製品市場投入時間を短縮し、システムの信頼性を向上させ、また、ボードの消費電力を最適化します(図4)。POL電源の出力電圧は、総合未調整誤差(TUE)0.25%というクラス最高の16ビットADCを使ってトリミング、マージニング、モニタリングされ、ボードの効率と長期的性能が向上します。POLの出力電圧を±0.25%の精度に維持できるので、負荷過渡応答に対応できるだけの十分な余裕を残しており(±3%のFPGAレール仕様に対して±2.75%)、必要なバイパスコンデンサ容量が大幅に減り、ボードスペースにも空きができます。電源出力電流は、検出抵抗、インダクタDCR、または電源のIMON出力を使って測定します。電圧と電流の測定値は内部で乗算され、POL出力指示値を得るのに便利です。

LTC2972には、電源シーケンシング、監視および、EEPROM障害ログのための機能が組み込まれています。シーケンシングは時間遅延を内部レジスタに書き込むことによって行うか、カスケード化されたパワーグッド信号によって行います。POLの入力電圧、出力電圧および、温度が、デジタル的に設定された下限閾(しきい)値と上限閾値を超えると、専用の高速コンパレータが障害の発生を知らせます。障害が発生するとEEPROMブラックボックス記録が開始されるので、故障分析が容易になる他、将来的なシステム改善の見通しを立てることができます。さらに、最初の障害コマンドはシステム障害の原因に関する追加的な情報も提供します。障害は他の電源やDPSMデバイスへ柔軟に伝達することができます。

LTC2972は、POLコンバータへの中間バス入力の電圧、電流、電力および、電力量を監視する機能を備えています。サーバおよび、データセンターの冷却コストと光熱費を削減するには、回路基板の使用電力と使用電力量をモニタリングして、その消費を管理、最適化、削減する必要があります。LTC2972は、パワーマネージメントデバイスや電力変換デバイスとの通信用の業界標準であるPMBusインターフェースを通じ、入力電力量(ジュール単位)と経過時間を使いやすい形で提供することにより、大量のポーリングと計算に要するホストの負荷を軽減します。これをLTC2972のPOL出力電圧、電流、電力のデジタル測定機能と組み合わせれば、パワーシステムの変換効率を長期的にモニタリングすることが可能になります。

各チャンネルでは、プログラマブルパワーグッドピン、あるいは汎用入出力(GPIO)ピンを使用できます。また、LTC2972を他のパワーシステムマネージャに接続すれば、3つ以上のレールのシーケンシングと障害管理を行うことができます。さらにI2C/SMBusインターフェース経由でPMBus対応コマンドを使用すれば、パワーシステムの柔軟なプログラミングとデータの読み出しが可能です。設定はLTpowerPlay開発環境を通じて行いますが、この環境はアナログ・デバイセズのすべてのDPSM製品に対応しています(図5参照)。ひとたび必要とされる特定用途用の構成で内部EEPROMをプログラムすれば、他に自律動作用のソフトウェアをコーディングする必要はありません。

まとめ

FPGAはあらゆるタイプの電子機器へ浸透し、ASICにとって代わる事態も発生していますが、それを取り巻くパワーシステムは複雑になってきています。アナログ・デバイセズは、その複雑なシステム管理の助けとなる幅広いDPSM製品を提供しています。これまでDPSMを使用したことがない場合でも、LTC2972を使用すればDPSMの能力を容易に導入し、デジタル処理ボード上のパワーシステムの複雑さを軽減することができます。

FPGAのリファレンス設計については、analog.com/FPGAをご覧ください。

Copyright © ITmedia, Inc. All Rights Reserved.

関連リンク

提供:アナログ・デバイセズ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2020年11月11日