SiCパワーMOSFETを採用した電源回路、配線レイアウトの考慮が高精度解析に不可欠:SiC採用のための電源回路シミュレーション(3)(4/4 ページ)

SiCパワーMOSFETを採用した電源回路の回路シミュレーションを実行する際は、設計したプリント基板の配線レイアウトを解析し、その寄生インダクタンスや寄生キャパシタンスを分布定数として高精度で抽出する必要がある。

放射ノイズの解析も可能に

ここまでの作業で、電子部品のデバイスモデルを含む電源回路のデータと、アプリケーションボードの配線レイアウトのSパラメータを統合することができた。この統合後のデータをキーサイトでは「サブサーキット」と呼んでいる。

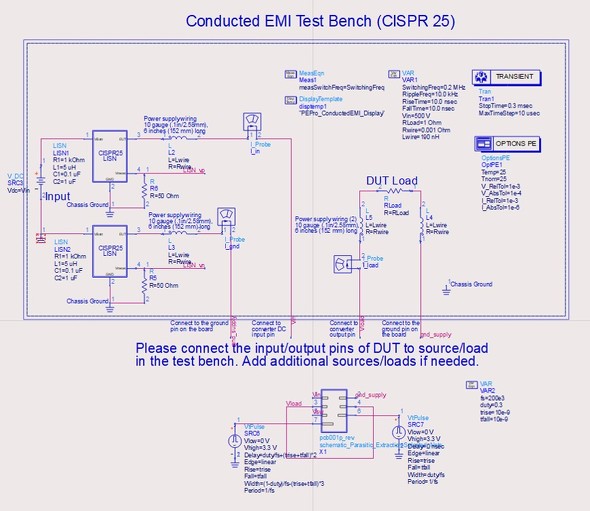

サブサーキットを使えば、電源回路に関するさまざまな解析が可能になる。解析を実行するには「テストベンチ」と呼ぶ機能を使う(図4)。テストベンチとは、仮想的な実験環境のことであり、その実験の対象がサブサーキットになる。ADS上でこのサブサーキットに対して、仮想的な信号源や負荷などを接続することでテストベンチが作成する。

このシミュレーションキットの中には、電源回路のスイッチング動作(電圧スパイクの解析)、伝導ノイズ、放射ノイズ(EMI)の解析に向けたテストベンチがあらかじめ用意されている。ユーザーは、これらのテストベンチにサブサーキットを設定するだけで上記の解析を簡単に実行できる。この3種類以外の解析が必要な場合は、ユーザーが独自にテストベンチを作成する必要がある。

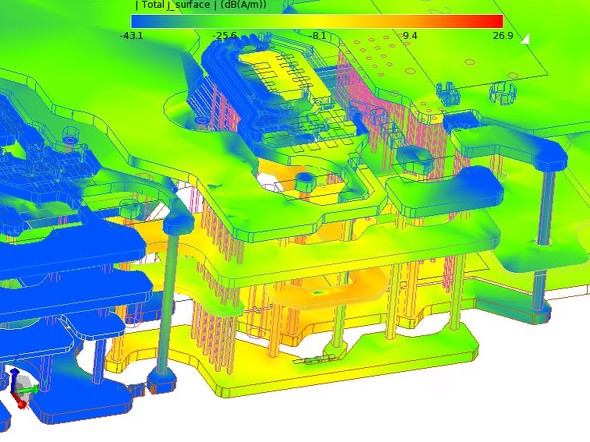

こうした解析を実行すれば、実際にアプリケーションボードを試作する前に、さまざまな特性を把握できると同時に、設計の問題点を発見できる。例えば、スイッチング動作の解析を実行すれば、スイッチングノードでの電圧/電流波形を確認できるため、電圧波形のリンギングの大きさや各配線の電流密度などを把握できる(図5、図6)。さらに放射ノイズや伝導ノイズの解析を実行すれば、その規制値「CISPR25」をクリアできるかどうかを確認可能だ。

図6:電流密度の解析結果[クリックで拡大] 出所:キーサイト・テクノロジー

テストベンチを使って各配線の電流密度を解析し、それをグラフィックス表示した結果である。電流密度が最も高い配線を赤色で、低い配線を青色で示した。

こうした解析でアプリケーションボードの問題を発見すれば、すぐに設計の修正に取り掛かれる。そして修正を加えたら、再度、解析を実行できる。設計の修正を施し、解析を実行して、特性を確認。こうした設計ルーティンを高速に回すことができるため、アプリケーションボードの配線レイアウトを短時間で最適化できるようになる。

これからのスイッチング電源回路設計

SiCパワーMOSFETを採用した電源回路の回路シミュレーションが抱える2つの課題。1つ目の課題であるデバイス・モデルの精度については、前述の通り、本連載の前回、前々回の記事で解決策を提示した。そして、もう1つの課題である配線レイアウトのモデリングについては、本稿で解決する方法を説明した。

今後、SiCパワーMOSFETを採用した電源回路が増加していくだろう。同時に、電源回路の設計現場でも、上記で示したような配線レイアウトを考慮した回路シミュレーターの活用が当たり前になっていくはずだ。

【著】

・佐々木広明(キーサイト・テクノロジー株式会社グローバルソフトウェア&サービス営業本部EDAアプリケーションエンジニアリング部)

・橋本憲良(同)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

SiCパワーMOSFETのデバイスモデル、オン時の容量考慮で精度が大幅向上

SiCパワーMOSFETのデバイスモデル、オン時の容量考慮で精度が大幅向上

スイッチング動作が極めて高速なSiCパワーMOSFETを用いた電源回路設計では、回路シミュレーションの必要性に迫られることになるが、従来のモデリング手法を用いたデバイスモデルでは精度面で課題があった。本連載では、この課題解決に向けた技術や手法について紹介する。 SiCパワーMOSFETのスイッチング特性、大電流/高電圧領域の測定で解析精度が向上

SiCパワーMOSFETのスイッチング特性、大電流/高電圧領域の測定で解析精度が向上

SiCパワーMOSFETのデバイスモデルの精度向上には、「大電流/高電圧領域のId-Vd特性」および「オン抵抗の温度依存性」を考慮しデバイスモデルに反映させることも重要となる。今回はこの2点に関する解説を行う。 電気自動車の充電インフラ

電気自動車の充電インフラ

電気自動車の充電インフラについて、規格や電力トポロジーをまとめる。さらに、SiCデバイスが鍵を握ることにも触れる。 1700V SiC MOSFETのパワーソリューション

1700V SiC MOSFETのパワーソリューション

マイクロチップ・テクノロジーは、1700V SiC MOSFETのダイ、ディスクリートおよびパワーモジュールを発表した。同製品群をIGBTから置き換えることで、充電ステーションの小型化やバッテリー駆動車両の走行距離、動作時間の延長が可能になる。 EV充電向けのSiC MOSFETモジュール

EV充電向けのSiC MOSFETモジュール

オン・セミコンダクターは、EV充電ステーション向けの1200VフルSiC MOSFET 2パックモジュール「NXH010P120MNF1」「NXH006P120MNF2」を発表した。プレーナー技術を活用し、18〜20Vの駆動電圧に対応する。 次世代EVや産業向け第3世代SiCパワーMOSFET

次世代EVや産業向け第3世代SiCパワーMOSFET

STマイクロエレクトロニクスは、第3世代SiCパワーMOSFETを発表した。電力密度や電力効率、信頼性を必要とする車載用および産業用途に適する。