高分解能コンバーターの設計におけるAFEの考慮ポイント:オペアンプの選択やノイズの影響など(2/2 ページ)

高分解能コンバーターを設計する際に考慮すべき、アナログフロントエンド(AFE)のポイントについて解説する。

フロントエンドのノイズが回路に与える影響

通常、ノイズ源は互いに相関関係がないため、RSS(二乗和平方根)で足し合わせることができます。

アナログフロントエンド部のノイズが高ければ高いほど、総ノイズ(RMS/二乗平均平方根)に対して支配的になります。5nVのノイズ源が別の3nVのノイズ源に加えられると、5.8nV(rms)となります。当然、どちらか大きい方が支配的になります。

感覚をつかむために、信号対雑音比(SNR)の合計を求めてみましょう。単純になるように、信号対雑音+歪み比は無視します。コンバーターのSNRは、通常はデシベル単位でデータシートに記載され、式(3)のように表すことができます。

(6.02*n) + 1.761 (3)

ここで、nは分解能つまりビット数です。

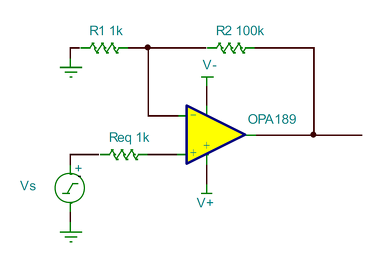

オペアンプ/PGA/INAのSNRを求めるには、まずRSSで総ノイズを計算します。図1をご覧ください。

ゲイン設定とフィードバック抵抗を別々に使用する代わりに、ノイズ計算では、Req抵抗で示される等価並列結合を使用できます。そのため、Req = 990Ωとなり、これは事実上、ほぼ1kΩです。

外付け抵抗の熱雑音を式(4)で表します。

enR=√4kTReq (4)

ここで、kはボルツマン定数であり、1.38×10−23m2 kg s−2 K−1と等しく、Tは298Kです。

熱雑音を簡易的に求めるために、式(5)を用います。

4√R [nV/√Hz] (5)

ここで、Rは抵抗値(キロオーム単位)です。1kΩ抵抗では4nV√Hzですが、100kΩの場合は室温25℃(298K)のとき40nV√Hzとなります。

TIのOPA189では、1kHzのときの電圧ノイズ密度(en)は5.2nV/√Hzであり、電流ノイズ密度は165fA/√Hzです。電流ノイズ寄与は、eni = 165×10−15×1×103 = 165×1012となります。

総ノイズ(en_total)は、式(6)のように表されます。

√en2+eni2+(enR)2 (6)

これは6.56nV/√Hzです。

出力のrmsノイズを求めるには、まず式(7)で定義される閉ループ帯域幅(fc)が必要です。

BW = GBP/NG (7)

ここで、GBPはゲイン帯域幅積、NGはノイズゲインです。値を当てはめると、式7は(14e6/101)となり、計算結果は139kHzとなります。

次に、総rmsノイズを式(8)で表します。

NG*en_total√NBW (8)

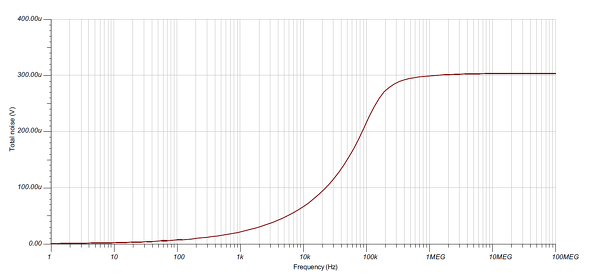

ここで、NGはノイズゲイン、NBWはノイズ帯域幅ですが、これはfc = 1.57×fc = 218kHzと定義されます。値を当てはめると、式(8)の結果は101*6.56×10−9√218000 = 310μVです。この場合、rmsノイズのシミュレーション結果は300μVを示していました。

オペアンプのSNRは、式(9)で求められます。

20*LOG(VFSR/(2*√2)/Erms) (9)

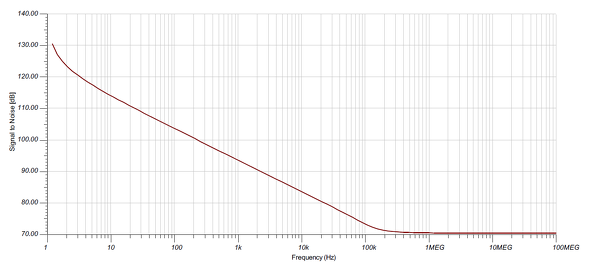

ここで、VFSRは2.5V、Ermsは前の式により310μVです。シミュレーション結果の70.6dBに対し、計算結果は71.3dBとなります。

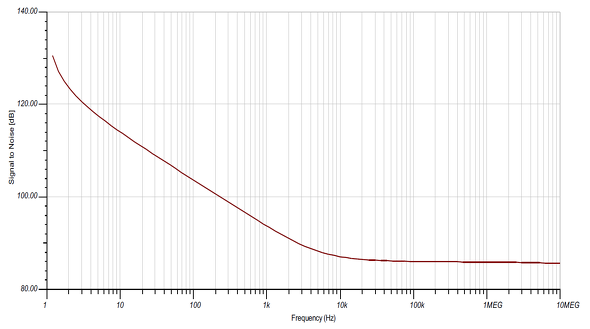

図2と図3はそれぞれ、総ノイズ(rms)とSNRのシミュレーション結果です。

式(10)を使うと、システム(オペアンプ、ADC、電圧リファレンス)の総SNRを求めることができます。

20*LOG√(10^(−71/10)+10^(−92/10)+10^(−85/10)) = −78dB (10)

フィードバックループにコンデンサーを配置することで、アンプのノイズを改善することが可能です。では、「カットオフ周波数をどこに設定するのか」という疑問が浮かんだ読者もいるかもしれません。

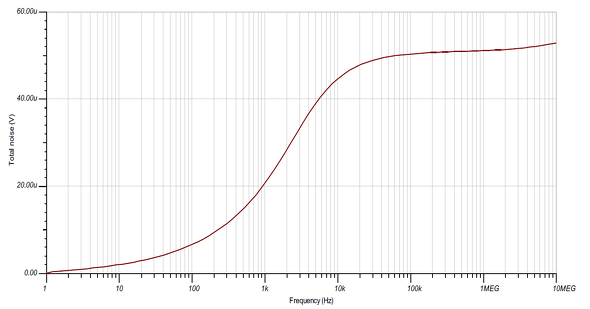

ノイズをシミュレーションする利点の1つ(正確にモデル化されていれば)は、総積分rmsノイズのプロット図から、ノイズの許容範囲に応じて、フィルターのカットオフ周波数を簡単に求められることです。

例えば、OPA189の出力ノイズを50μVに減らしたい場合、フィルターのカットオフ周波数をfc = 6kHz/1.57に設定します。

コンデンサーでフィードバック抵抗でのノイズ帯域幅を減らすために、1/(2π(6000/1.57)(100000))としてコンデンサー値を計算すると、416pFとなります。

このコンデンサーを配置した場合、総rmsノイズは50μVです。図4と図5から分かるように、オペアンプのSNRは、15dB改善して86dBになります。式(10)を使用すると、総SNRは82dBになっています。

高分解能コンバーターを設計するときに考えなければならないパラメータは他にもあり、この記事ではカバーしきれないほどです。適切なデバイスを自信をもって選べるようになるには、PGAや、オペアンプ、INA、その他のアナログフロントエンド部品と、そのプロセス技術を十分に調べることが役に立ちます。

バイポーラ入力オペアンプでは、かなり高い入力バイアス電流と電流ノイズが現れる傾向がありますが、スーパーベータトランジスタを使うことで大幅に低減される場合があります。

入力バイアス電流キャンセル付きのオペアンプを探すときは注意が必要です。電流ノイズの計算結果は、キャンセルなしのIbの値で計算したときよりも約41%上昇します。検討中のアンプがキャンセル方式を用いているかどうかを簡単に見分けるには、データシートの仕様表を確認してください。±記号があれば、そのアンプはキャンセル方式を用いています。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

非補償型オペアンプの基本を知る

非補償型オペアンプの基本を知る

ユニティゲインでも安定に動作するよう内部補償されたオペアンプには、ユーザーにとって、より容易に安全な回路を設計できるというメリットがある。しかし、そうした「完全補償型オペアンプ」では、AC性能の主要部分を犠牲にしていることも事実だ。本稿では、この種の製品とは異なる方針で設計された「非補償型オペアンプ」の概要とそのメリットについて解説する。 半導体(5) ―― 実際に経験した不良と対策(IV)

半導体(5) ―― 実際に経験した不良と対策(IV)

今回も前回に引き続いて筆者が経験した不良について説明していきます。加えて当方で半導体の使い方を間違えた事例も説明しますので、本稿での事例を基に再発防止に役立てていただければよいかと思います。 電磁気学入門(4)コアレス〜相互インダクタンス損失と渦電流損失

電磁気学入門(4)コアレス〜相互インダクタンス損失と渦電流損失

電磁気学入門講座。今回は「相互インダクタンス損失」と「渦電流損失」について説明していきます。 GaNパワートランジスタとは

GaNパワートランジスタとは

省エネ化/低炭素社会のキーデバイスとして、化合物半導体である窒化ガリウム(GaN)を用いたパワー半導体が注目を集めている。本連載では、次世代パワー半導体とも称されるGaNパワー半導体に関する基礎知識から、各電源トポロジーにおけるシリコンパワー半導体との比較まで徹底解説していく。第1回である今回は、GaNパワートランジスタの構造や特長、ターゲットアプリケーションなどについて説明する。 ブリッジレス方式トーテムポール力率補正コントローラーで、高いAC-DC電力変換効率を達成する手法

ブリッジレス方式トーテムポール力率補正コントローラーで、高いAC-DC電力変換効率を達成する手法

AC-DC変換を行う変換器は、エネルギー送電網に設置されている最も一般的な負荷の一つになっています。本稿では、ブリッジレス方式トーテムポール力率補正コントローラーで、高いAC-DC電力変換効率を達成する手法について解説します。 SiCパワーMOSFETのデバイスモデル、オン時の容量考慮で精度が大幅向上

SiCパワーMOSFETのデバイスモデル、オン時の容量考慮で精度が大幅向上

スイッチング動作が極めて高速なSiCパワーMOSFETを用いた電源回路設計では、回路シミュレーションの必要性に迫られることになるが、従来のモデリング手法を用いたデバイスモデルでは精度面で課題があった。本連載では、この課題解決に向けた技術や手法について紹介する。