超定番タイマーIC「555」の周波数直線性を改善する:Design Ideas アナログ機能回路(2/2 ページ)

今回の回路アイデアは、超定番タイマーIC「555」の周波数直線性を改善するものだ。

デバイス内部に暗黙の時間遅延が存在

実際に起きていることは単純で、明示されている121nsの外付けRC時定数に加えて、デバイス内部に次のような暗黙の時間遅延(Td)が存在しているのだ。

Td=1/3MHz−1/8.28MHz=333ns−121ns=212ns

この212nsの内部遅延は、低周波から中程度の周波数ではデータシートの定番計算式を十分に正確なものにしているが、限界に近いマルチメガヘルツ領域まで性能を引き上げたいのであれば、無視できなくなる。従って、高周波で実用的な精度を持つFOO予測式は、次のような形になる。

FOO=1/(Vth Ct/Ic+Td)=1/(3.33v Ct/Ic+212ns)

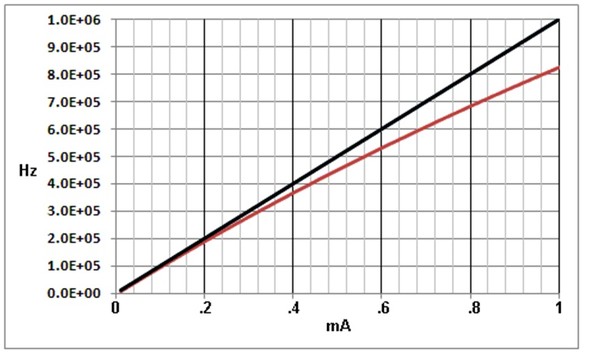

この式をプロットすると、図2の赤い右下がりの曲線が得られ、10mAで20%を超える誤差が生じる。本来なら1MHzになるはずが、実際には約800kHzにしかならない。これはかなり残念な結果だ。

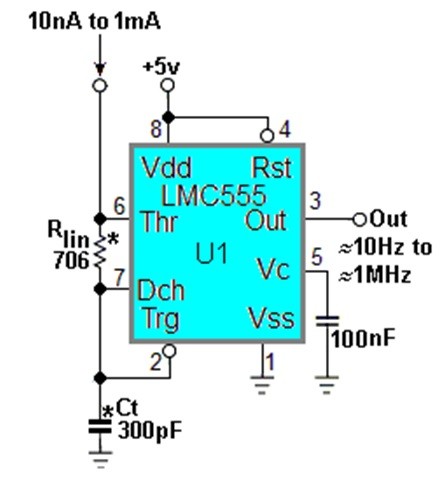

幸い、この問題には対策があり、しかも驚くほど簡単だ。必要なのは、Dch(discharge)ピンとThr(threshold)ピンの間に抵抗Rlinを1つ追加するだけだ。これはThrピンをIcRlinに等しい電圧だけ上方にバイアスし、電流対周波数の関係を直線化する働きをする。これによって、のこぎり波状のタイミングランプの継続時間は次の分だけ短縮される。

T=IcRlin/(Ic/Ct)=RlinCt=Td

これによって、555の内部遅延を打ち消すことができる。

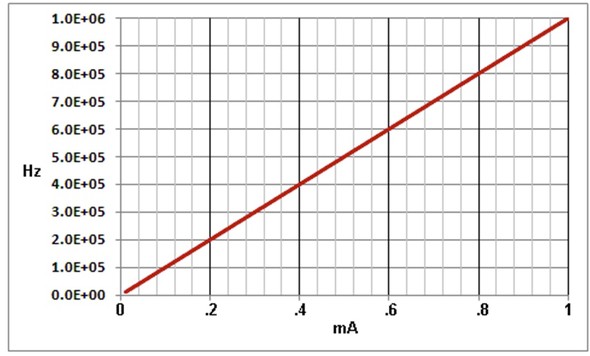

それゆえ、図3に示すようにRlinCt=TdとなるようRlinを選べば、図4に示す通り、制御電流の全範囲にわたって非直線性の補償は(少なくとも理論上は)完全になる。すなわち、下記となる。

FOO=1/(Vth Ct/Ic+212ns−Td)=1/(3.33vCt/Ic+212ns−212ns)=1/(3.33vCt/Ic)=Ic 1000MHz

……理論上は、こうなる。

そこで疑問が生じる。この理論から実用的な成果を得られるのか、という点である。これについては近いうち詳しく述べたい。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルター回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバー】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

10Hz〜1MHzで周波数を可変する「のこぎり波発振回路」

10Hz〜1MHzで周波数を可変する「のこぎり波発振回路」

発振回路を用いてアナログののこぎり波(サートゥース)波形を生成する方法は数多く存在する。本稿では、単一の電源電圧レールを用い、10Hz〜1MHzの範囲で周波数を可変できるバッファー付き信号を生成する方法を紹介する。 定番「TL431」2個の合わせ技、多用途な電流ミラー

定番「TL431」2個の合わせ技、多用途な電流ミラー

今回の回路アイデアは、シャント電圧レギュレーター「TLx431」を2個組み合わせて、プログラマブルな利得を持つ電流ミラーを作るというものだ。 万能のタイマーIC「LMC555」がまだ驚かせる、可変抵抗1個で4桁可変

万能のタイマーIC「LMC555」がまだ驚かせる、可変抵抗1個で4桁可変

定番のCMOSアナログタイマー「LMC555」の周波数を可変抵抗1個で10Hz未満から100kHz超まで広げる回路を紹介する。 多数の信号線に対するコモンモード電圧対策

多数の信号線に対するコモンモード電圧対策

コモンモード電圧(CMV)に起因する誤動作や性能劣化を防ぐため、信号の入出力に差動型の計装アンプを使用する手法が用いられる場合が多い。しかし、この方法には信号線ごとに専用のアンプ回路を要するという欠点がある。今回は、この欠点を改善しようと考案した回路を紹介する。 PLDを使ったPWM信号発生器

PLDを使ったPWM信号発生器

任意の分解能のPWM(Pulse Width Modulation)信号を発生させるPLD(Programmable Logic Device)コードを紹介する。 チューニングが不要なオーディオ用LPFの設計法

チューニングが不要なオーディオ用LPFの設計法

オーディオ向けの低域通過フィルター(LPF)は、処理の初段でのS/N比(信号対雑音比)を最大にできるよう、ゲイン調整機能を有している必要がある。さらに、低コスト化のためには、製造過程における調整工程をなくさなければならない。そこで本稿では、受動素子の誤差がフィルター特性に及ぼす影響を低減し、なおかつ低コストでの実現が可能な高次フィルターの設計方法を紹介する。