前回(第14回)は、「デジタル・アシスト・アナログ(DAA:Digitally Assisted Analog)技術」の課題や問題点などを解説しました。今回は、DAA技術の導入がアナログICにどのような未来をもたらすかを展望します。

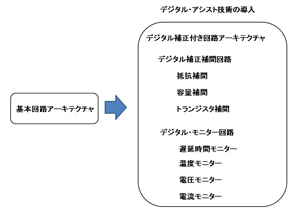

まず明確に分かっていることは、アナログICとミクスドシグナルICではDAA技術の導入がさらに進んでいくことです。デジタル・アシスト回路を導入するIC製品が増えるとともに、ICチップ当たりで導入するデジタル・アシスト回路の数が増えていくでしょう。アナログICベンダーが「ハイパフォーマンスアナログ(HPA)」と呼んでいる最先端のミクスドシグナルICでは、デジタル・アシスト回路の導入が標準的なものとなるに違いありません。

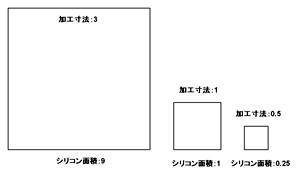

その大きな理由は、半導体製造技術の微細化が進めば進むほど、CMOSの回路が小さくなり、同じシリコン面積に詰め込めるデジタル回路の規模が大きくなるからです。同じ量産コストでも、利用できるデジタル回路の規模が大きくなる。かつてはコストが高くて採用できなかった大規模なデジタル回路が、新しい世代(より微細化が進んだ世代)のCMOS ICでは採用可能になります。半導体製造技術が1世代進んだときに、同じシリコン面積に詰め込めるMOSトランジスタの数はおおよそ2倍です。これは、2世代進むと4倍、3世代進むと8倍になるということを意味します。

次に分かっていることは、大規模なIC、いわゆるSoC(System on a Chip)と呼ばれている半導体チップは、そのほとんどがアナログ回路とデジタル回路を混載したミクスドシグナルICとなっていくことです。

現在、最先端のCMOSロジック回路はおおよそ40nmくらいの微細加工技術を使っています。一方でバイポーラ・アナログ回路では、130nmくらいの微細加工技術を使っていることが少なくありません。両者を同じ製造コスト(シリコン面積)で実現できるトランジスタ数で比較すると、およそ10倍の開きがあります。

この結果、システムを構成するほとんどの回路は、ワンチップのシリコン・ダイで実現できるようになります。CMOSアナログは、原理的にはCMOSロジックと同じ密度でトランジスタを詰め込めますので、高周波回路や電源回路などのCMOSアナログ回路も、SoCに混載されるようになっていきます。すでに45nmクラスのSoCでは、このようなミクスドシグナル回路となっていることが珍しくありません。

またCMOSアナログは、その性能がバイポーラ・アナログに比べると劣る傾向があります。そこでDAA技術を導入することで、総合性能を高めるようになっていきます。

回路技術者の役割が増大する

そして半導体エンジニア(技術者)の仕事という点では、回路技術者の役割が高まるということです。前回にご説明したように、DAA技術を導入したアナログ回路を設計できるのは、アナログ回路の知識と経験に加え、デジタル回路の知識を備えた技術者です。デジタル・アシスト回路のほとんどは、デジタル信号処理理論やデジタル制御理論などを必要としています。

デジタル・アシスト回路には「これが唯一の正解」という回路は存在しません。もっともデジタル・アシスト回路に限らず、アナログ回路でもデジタル回路でも「これが唯一の正解」という回路はありません。求められているのは「性能やコストなどの要求仕様を満たす回路」であり、要求仕様を満たす回路はいくつも存在します。

ただしアナログ回路でもデジタル回路でも、半導体回路技術の歴史の中で生まれてきた、重要かつ普遍的な回路は存在します。回路技術の教科書を開くと、そのような回路はいくつも掲載されています。

デジタル・アシスト回路の登場は、回路技術の発展性を一段と広げました。なぜなら、既存のアナログ回路アーキテクチャと、回路技術者が考案したアシスト回路のアーキテクチャを組み合わせることで、新しい回路アーキテクチャが生まれるからです。DAA技術は回路アーキテクチャの多様化を促し、アナログICやミクスドシグナルIC、SoCなどを一段と進化させることになるでしょう。

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.