プリエンファシスとデエンファシス

プリエンファシスとデエンファシスとは、データ伝送におけるシグナル・コンディショニング(信号調整)技術の一種である。LVDS(Low voltage differential signaling)やCML(Current Mode Logic)などの高速差動伝送方式を用いるシリアル・インターフェースで盛んに利用されている。

高速データ伝送に不可欠な技術

一般に信号伝送路は、ローパス・フィルタ(低域通過フィルタ)として機能する。従って、そこを伝搬する信号の高周波成分は減衰してしまう。伝送距離が長ければ長いほど、周波数が高ければ高いほど減衰量は大きくなる。このため、高速な信号を長距離伝送する際は、シンボル間干渉(ISI:Inter-symbol Interference)ジッタが大きくなり、正確に情報を使えることが難しくなる。

そこで登場するのがプリエンファシスとデエンファシスという2つのシグナル・コンディショニング技術である。いずれも、高速シリアル・インターフェースの送信回路で実行する点は同じだ。しかし、送信信号に対する調整方法が異なる。

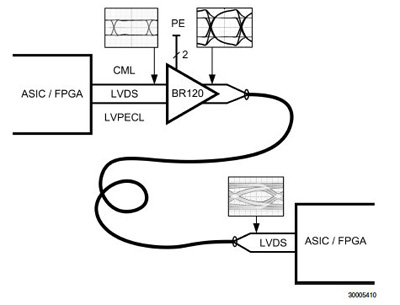

プリエンファシスは、差動伝送路で減衰してしまう高周波成分を送信回路であらかじめ追加して伝送する方式である(図)。一方のデエンファシスは、差動伝送路で減衰する高周波成分に合わせて、送信回路で低周波成分を削って伝送する方式である。このように調整方法は異なるが、いずれの方式とも、受信回路ではきれいなアイ・パターンが得られるようになる。つまり、ISIジッタを大幅に低減することができるわけだ。

プリエンファシスとデエンファシスは、同様な効果が得られるが、どのように使い分ければ良いのだろうか。ポイントは、電圧振幅の大きさにある。プリエンファシスは高周波成分を追加するため、電圧振幅が大きくなる。一方、デエンファシスは低周波成分を削るため、電圧振幅が小さくなる。電圧振幅が大きいと、論理値の「0」と「1」の間の遷移時間が長くなる。従って、高速な信号伝送に適さない。目安は、1〜3Gビット/秒である。それ以下であれば、プリエンファシス、それ以上であればデエンファシスがプロセスのエッジレート振幅の兼ね合いで適しているといえる。

プリエンファシスを搭載した高速シリアル・インターフェース・チップの代表例としては、「DS25BR120」がある。これは、3.125Gビット/秒の伝送速度に対応したLVDSバッファICである。プリエンファシス機能を搭載する。プリエンファシスのブースト・レベルは0dB、3dB、6dB、9dBの中から選択できる。FPGAやASICなどから出力されたLVDS/CML信号を長距離伝送する用途などに向ける。

テキサス・インスツルメンツのインタフェース製品ラインアップ

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.