SAR(逐次比較)

SARとは、ADコンバータを実現する回路手法の一つ。「Successive Approximation Register」の頭文字を取った言葉である。日本語では、逐次比較と訳される。

ADコンバータを実現する回路手法はいくつかある。代表的な手法としては、SAR方式のほか、ΔΣ方式やパイプライン方式、フラッシュ方式などが挙げられる。これらの方式はそれぞれ得手不得手がある。SAR方式では、10〜18ビットと比較的高い分解能で、数100k〜数10Mサンプル/秒と中速のサンプリング速度のADコンバータを実現できる。さらに、直流(DC)精度が高いADコンバータが得られるというメリットもある。ちなみに、最も分解能が高いADコンバータを得られるのはΔΣ方式、最も高いサンプリング速度が実現できるのはフラッシュ方式である。

アナログ入力をシリアルに比較

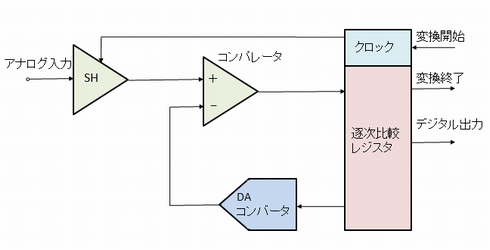

それでは、SAR方式の実現方法を説明しよう。一般に、SAR方式のADコンバータは、サンプル・ホールド(SH)回路とコンパレータ(比較器)、DAコンバータ、逐次比較レジスタ、制御回路などから構成される(図1)。これらを使って、1ビットずつ順番(シリアル)に比較していくことで、デジタル出力を決定するわけだ。

図1 SAR方式を採用したADコンバータの内部構成

SAR方式のADコンバータの一般的な内部構成である。サンプル・ホールド(SH)回路とコンパレータ(比較器)、DAコンバータ、逐次比較レジスタ、制御回路などから構成される。

具体的には、最初にDAコンバータの最上位ビット(MSB:Most Significant Bit)だけを1に、残りは0に設定して、アナログ入力信号と比較する。この結果、アナログ入力信号の方が大きければMSBは1に、小さければ0になる。次に、MSBよりも1つ位の小さいビットだけを1に、残りを0にして、同様の比較を行う。これを複数回繰り返して、最下位ビット(LSB:Least Significant Bit)まで決めれば、変換作業は終了する。DAコンバータの分解能がnビットならば、比較の回数はn回となる。こうして得られたDAコンバータのnビットのコードがADコンバータのデジタル出力となるわけだ。

なお、入力段に置くサンプル・ホールド回路は、アナログ入力信号を一時的に格納する役割を果たす。SAR方式のADコンバータでは、シリアルに比較する方式を採用するため、AD変換の作業中にアナログ入力信号が変化してしまうと正確な結果が得られないためだ。

逐次比較方式を採用したADコンバータの例としては、テキサス・インスツルメンツ(TI)の「ADS8028」がある。分解能は12ビットで、最大サンプリング速度は1Mサンプル/秒。特長は、精度が高いことにある。積分非直線性誤差(INL)と微分非直線性誤差(DNL)はいずれも±0.5LSBと小さい。12ビットのノー・ミッシング・コードを保証する。集積度も高い。アナログ入力のチャネル数は8個で、温度センサや9チャネル入力のマルチプレクサ、低温度ドリフトの基準電圧源などを搭載した。消費電力は、1Mサンプル/秒動作時に17mWと小さい。アプリケーションは、プログラマブル・ロジック・コントローラ(PLC)や工業用プロセス機器、通信機器、電源監視装置など。

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2014年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.