半導体の温故知新(4)――IBM30億ドル投資の裏にCMOSの凄さあり:津田建二の技術解説コラム【歴史編】

2014年7月、IBMがポストCMOSの半導体技術に今後5年間に渡り30億ドル(3000億円)を投資すると発表しました。なぜIBMはポストCMOS技術の開発に30億ドルも投資するのでしょうか? 半導体技術としてあまりにも優れているCMOSの代替技術を探しているのです。

うわさは“うわさ”に過ぎなかった

2014年7月10日、IBMがポストCMOSの半導体技術に今後5年間に渡り30億ドル(3000億円)を投資すると発表しました。その1カ月ほど前には、IBMは半導体ビジネスを手放してGlobalFoundriesをはじめとするファウンドリ企業に売却するだろうとうわさされていました。うわさはどの国でも”うわさ”に過ぎません。うわさは真実ではないので、ちょっとした想像だけが独り歩きすることが多く、結局間違いだったという情報もよくあります。今回のケースはまさに“うわさ”だったようです。

なぜIBMはポストCMOS技術の開発に30億ドルも投資するのでしょうか? それは、半導体技術としてCMOS基本回路があまりにも優れていたことに対する裏返しでもあります。IBMが投資する理由を述べる前に、これまでのCMOS技術がいかに優れていたかについて復習しましょう。IBMはCMOSの代替技術を探しているのです。

CMOSはいかに優れているのか

CMOS回路は1980年代に確立され、以来あらゆる半導体集積回路に使われてきました。既に40年以上の実績があります。その最大のメリットは、High(1)とLow(0)のいずれの状態にとどまっていても電流が流れない(リーク電流のみ)、ことです。1か0の切り替えの時だけに電流が流れます。このため、頻繁に1、0を切り替える、すなわち周波数を高くすると電流は増加します。クロック周波数を上げていくと、CMOS ICの消費電力は正比例して増えるのはこのためです。

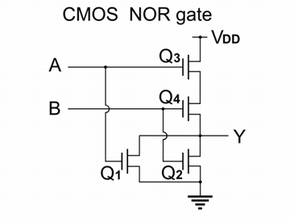

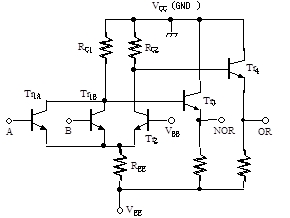

図1は、CMOSのNORゲート回路とECL(Emitter coupled logic)のOR/NOR回路を示したものです。この図にはありませんが、TTL(Transistor-transistor logic)と呼ぶゲート回路が一般的なゲート回路(標準ロジック)として普及していました。TTLの速度はそれほど速くはないのですが、ECLロジックよりも消費電力は低かったのです。汎用性が高く、回路構成がやや簡単だったために普及していました。

これに対して、ECLは速度が最も速いのですが、消費電力は大きすぎました。ECLは差動回路を基本としていますので、参照電圧が必ず必要です。入力電圧側か基準電圧側か、いずれかに流れる電流の経路を変えるだけで1、0を判別していました。いずれの場合も常に電流は流れていました。トランジスタはバイポーラ型ですが、飽和領域で電流を流さないため動作速度が速かったのです。また、電流経路を切り替えるだけの差動回路ですから、信号振幅は小さくて済みました。

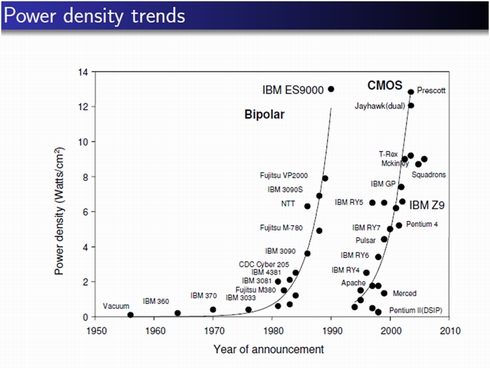

ECLは1970年代から1980年代の始めにかけて大型コンピュータのCPUをはじめとする演算部に使われました。しかし、集積するトランジスタが増えていくのにつれ、消費電力も増加してきました。このため、ECLは1990年ごろから、もっと消費電力の少ないCMOSにとって代られました(図2)。

主流になれなかったロジックとして、nチャンネルMOSやpチャンネルMOSだけの基本回路もありました。1、0どちらかのロジックでは電流が流れていたため、トータルでの消費電流が大きかったのです。

CMOSロジック回路は、pチャンネルMOSFET(図1ではQ3とQ4)とnチャンネルMOSFET(同Q1とQ2)を直列に接続した構造を持ちます。電源Vcc近くにpMOS、接地の近くにnMOSが配置されています。両MOSFETのゲートは共通で、入力のゲートがHighならば、pMOSには電流が流れず、nMOSに流れ、nMOSのドレインは接地レベルになり出力ノード(図1の左のY)はLowになります。この状態では、電源電圧から接地にかけて電流は流れません。

逆に、入力ゲートがLowならばpMOSに電流が流れ、nMOSには流れません。このため出力ノードYはHighになります。この構造ではpMOSとnMOSの両方に電流(貫通電流と言います)が流れることはありません。つまりHighでもLowでも状態にとどまっていれば、貫通電流は流れないため、消費電力が少ないのです。ただし、リーク電流はわずかに無視できるほど流れますが、微細化が進むのにつれて、リーク電流は増加する傾向にあります。

リーク電流、クロックの頭打ち

CMOS技術は1990年代から2010年にかけて、マイクロプロセッサやメモリ、ロジック、アナログなどさまざまな回路に本格的に使われてきました。ただし、CMOSは動作周波数を上げていくにつれ、増加してきます。このため、2000年代中ごろからクロック周波数を上げずに性能を伸ばす方法として、マルチコア技術が使われるようになってきました。いわば並列処理プロセッサです。演算処理を並列してこなすことにより性能を上げる手法です。

クロック周波数を上げることは、もはや頭打ちになっています。消費電力が許容範囲を超えたため、2〜3GHzが実用上、最大になっています。もちろん、液体窒素を使って冷却しながら8GHzを超えるクロックでプロセッサを動作させたという単なる記録作りの試作例はありますが、実用的ではありません。

製品のマイクロプロセッサは、高速演算が必要ではない場合(例えばグラフィックス描画など、GPUに頼る場合)に、電圧やクロック周波数を下げる手法がよく使われています。それぞれ、電圧ゲーティング、クロックゲーティングと呼ばれています。電圧の2乗で消費電力は下がり、クロック周波数は比例して消費電力を下げます。さらに、プロセッサに任せる仕事によって、使わない回路の電源を切るという操作もあります。結局、現在のCMOS技術では、回路的な工夫や、リーク電流を減らすためのプロセス技術によって、少しずつ消費電力を下げています。

CMOSを超えるため

これ以上、消費電力を大きく下げるデバイスは今の所ありません。だから、IBMが今後5年間に渡り、CMOSを超えるデバイス(もはや3端子のトランジスタではないかもしれません)を開発しようとしています。大きく分けて2方向の開発戦略を持っています。1つは、CMOSとは違う新しいロジックとして、デバイス1個でゲート数個分の基本回路を開発します。量子コンピュータが目指すものはこの基本ロジックです。さらにCMOSの配線やトランジスタの消費電力を下げるポストCMOS構造の半導体、グラフェンやカーボンナノチューブ(CNT)などの新材料を用いたトランジスタなども含まれます。

もう1つの方向は、現状のノイマン型コンピュータと同じ原理で動作するプロセッサとは全く異なる、新原理の計算機を開発することです。目標としているのは、人間の頭脳をモデル化し、ニューロン(神経細胞)とシナプス(神経の交差点)を備えたプロセッサです。100億個のニューロンと100兆個のシナプスを持つニューロシナプティックコンピュータを作製する計画を持っています。

この2つの技術を将来のコンピュータシステムにIBMが投資しようとしているのです。

Profile

津田建二(つだ けんじ)

現在、フリー技術ジャーナリスト、セミコンポータル編集長。

30数年間、半導体産業をフォローしてきた経験を生かし、ブログや独自記事において半導体産業にさまざまな提言をしている。

提供:ルネサス エレクトロニクス株式会社 / アナログ・デバイセズ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2015年5月31日

Copyright © ITmedia, Inc. All Rights Reserved.