چ·“®گMچ†“`‘—‚جƒپƒٹƒbƒg پ\پ\ژg—p‚³‚ê‚ؤ‚¢‚é‹Zڈp‚ئ’چˆس“_پFچ‚‘¬ƒVƒٹƒAƒ‹“`‘—‹Zڈpچuچہپi2پjپi4/4 ƒyپ[ƒWپj

چ‚‘¬ƒVƒٹƒAƒ‹“`‘—‹Zڈp‚ة‚آ‚¢‚ؤٹî‘b‚©‚çٹw‚ش–{کAچعپB2‰ٌ–ع‚حپAچ·“®گMچ†“`‘—‚ج“ء’¥پAƒپƒٹƒbƒg‚ةڈإ“_‚ً“–‚ؤپAژg—p‚³‚ê‚ؤ‚¢‚é‹Zڈp‚â’چˆس“_‚ة‚آ‚¢‚ؤ‰ًگà‚µ‚ؤ‚¢‚«‚ـ‚·پB

ƒپƒٹƒbƒg5پj•s—vçtژثƒmƒCƒY‚ھڈ¬‚³‚¢

پ@‘Oڈq‚µ‚½‚و‚¤‚ةCMOSƒچƒWƒbƒNڈo—ح‚حƒXƒCƒbƒ`ƒ“ƒO“®چى‚ًچs‚ي‚ب‚¢Œإ’èڈَ‘ش‚إ‚حپA“d—¬‚ح‚ظ‚عڈء”‚ꂸ•ْژثƒmƒCƒY‚àڈ‚ب‚¢‚إ‚·‚ھپAƒXƒCƒbƒ`ƒ“ƒO‚إGndپEVddٹش‚ةٹر’ت“d—¬‚ھ—¬‚êپAٹر’ت“d—¬‚ھ—¬‚ê‚éژüٹْ‚جژü”gگ”‚إٹî”آ‚جGndپEVddƒvƒŒپ[ƒ“‚ً—h‚炵‚ـ‚·پB‚±‚ج“®چى‚ھ“ء’èژü”gگ”‚إƒsپ[ƒN‚ًژ‚آ•s—vçtژثƒmƒCƒY‚جŒ´ˆِ‚ئ‚ب‚è‚ـ‚·پB

پ@LVDSچ·“®ƒhƒ‰ƒCƒo‚حگ}15-2‚ج’è“d—¬Œ¹‹ى“®‚ج•ûژ®‚ج‚½‚ك’لڈء”ï“d—ح‚إپACMOSƒچƒWƒbƒNڈo—ح‚جƒXƒCƒbƒ`ƒ“ƒO“®چى‚إ‹N‚±‚é‘ه‚«‚بٹر’ت“d—¬‚à‘¶چف‚µ‚ؤ‚¢‚ـ‚¹‚ٌپB

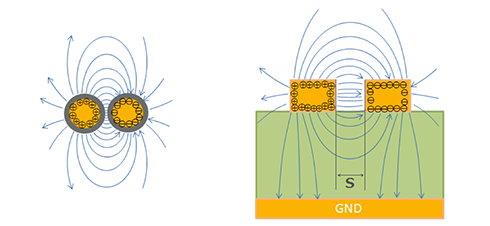

پ@‚ـ‚½چ·“®‚ج“`‘—‚إ‚حپAگ}17‚ج‚و‚¤‚ةƒPپ[ƒuƒ‹‚âٹî”آڈم‚إ2–{‚ج“±‘ج‚ً“dژ¥‹C“I‚ةŒ‹چ‡‚µچ‚‘¬‚ةگMچ†‚ً“`‘—‚µ‚ؤ‚¢‚ـ‚·پB‚±‚جچ·“®ٹشŒ‹چ‡‚ً‹‚‚·‚邱‚ئ‚إپA•ْژث‚³‚ê‚éƒRƒ‚ƒ“ƒ‚پ[ƒhƒmƒCƒY‚ً—}‚¦‚邱‚ئ‚ھ‰آ”\‚إ‚·پB

پ@چ·“®“`‘—کH‚ًگفŒv‚·‚éچغ‚حپAپ{‚ئپ|‚ج2–{‚جچ·“®ƒ‰ƒCƒ“ٹش‚ج‹——£پiSپj‚ً‹·‚‚·‚邱‚ئ‚إŒ‹چ‡‚ً‹‚‚µپAچ·“®گMچ†‚©‚ç‚ج•s—vçtژث‚ًŒ¸‚点‚ـ‚·پB‚½‚¾‚µƒhƒ‰ƒCƒo‘¤‚ج“dŒ¹‚ة“ü‚éƒmƒCƒY‚حپAڈo—ح‚جچ·“®2–{‚ةƒRƒ‚ƒ“ƒ‚پ[ƒhƒmƒCƒY‚ئ‚µ‚ؤڈdڈô‚³‚êپA•s—vçtژثƒmƒCƒY‚جŒ´ˆِ‚ئ‚ب‚è‚ـ‚·پB

پ@‘و2‰ٌ–ع‚حچ·“®گMچ†“`‘—‚ةژg—p‚³‚ê‚ؤ‚¢‚é‹Zڈp‚ئ”¼“±‘ج‚ج“®چى‚ًگà–¾‚µ‚ـ‚µ‚½پB•،گ”‚ج‹Zڈp‚ً‘g‚فچ‡‚ي‚¹‚ؤپAˆہ’肵‚½چ‚‘¬“`‘—‚ًچs‚ء‚ؤ‚¢‚邱‚ئ‚ھ—‰ً‚إ‚«‚½‚ج‚إ‚ح‚ب‚¢‚إ‚µ‚ه‚¤‚©پB

پ@ژں‰ٌپi‘و3‰ٌپj‚ح‘م•\“I‚ب•¨—‘w‚إ‚ ‚éLVDSپAPECLپACML‚ئگع‘±•û–@‚ة‚آ‚¢‚ؤگà–¾‚µ‚ؤ‚¢‚«‚ـ‚·پB

•MژزProfile

‰حگ¼ٹپi‚©‚ي‚ة‚µپ@‚à‚ئ‚س‚فپjپ^ƒUƒCƒ“ƒGƒŒƒNƒgƒچƒjƒNƒX ƒVƒjƒAƒGƒLƒXƒpپ[ƒg

پ@ƒiƒVƒ‡ƒiƒ‹ƒZƒ~ƒRƒ“ƒ_ƒNƒ^پ[ƒWƒƒƒpƒ“‚âƒWƒFƒiƒ€ƒWƒƒƒpƒ“‚ب‚اپA25”N‚ة‚ي‚½‚èچ‚‘¬’تگMŒn”¼“±‘ج‚جگ»•iٹJ”پEƒTƒ|پ[ƒg‚¨‚و‚رƒ}پ[ƒPƒbƒg‚جٹJ‘ٌ‚ةڈ]ژ–پB“`‘—کH‚ًٹـ‚ٌ‚¾”¼“±‘ج‚جچ‚‘¬گفŒvژè–@‚ھٹm—§‚³‚ê‚ؤ‚¢‚ب‚¢ژ‘م‚ةپALVDSƒIپ[ƒiپ[ƒYƒ}ƒjƒ…ƒAƒ‹‚جچىگ¬‚ب‚اپA“¯ƒ}پ[ƒPƒbƒg‚جگ¬’·پE•پ‹y‚ةٹٌ—^‚µ‚ؤ‚«‚½پB

پ@Œ»چف‚ح“ْ–{‚جSerDesگ»•iٹJ”‚جگو‹ىژز“I‘¶چف‚جƒUƒCƒ“ƒGƒŒƒNƒgƒچƒjƒNƒX‚إپAƒvƒچƒ_ƒNƒgƒ}پ[ƒPƒeƒBƒ“ƒOپEٹJ”ژx‰‡‚âگlچقˆçگ¬‚ب‚ا‚ًچs‚ء‚ؤ‚¢‚éپB

Copyright © ITmedia, Inc. All Rights Reserved.

ٹضکA‹Lژ–

PCIeپAUSBپAEthernetپAHDMIپALVDS‚ب‚اچ‚‘¬“`‘—‹Zڈp‚جٹî–{‚ً—‰ً‚·‚邽‚ك‚ة

PCIeپAUSBپAEthernetپAHDMIپALVDS‚ب‚اچ‚‘¬“`‘—‹Zڈp‚جٹî–{‚ً—‰ً‚·‚邽‚ك‚ة

–{کAچع‚إ‚حپA‚³‚ـ‚´‚ـ‚بچ‚‘¬’تگM‹Kٹi‚ةژg—p‚³‚ê‚ؤ‚¢‚镨—‘w‚جژd‘g‚ف‚âگ«”\پASerDes‚ج‹@”\‚â“ء’¥‚ئ‚»‚جژي—قپAچ‚‘¬“`‘—‚إ‚جژه—v‚بƒpƒ‰ƒپپ[ƒ^پ[پA“`‘—کH‚ًٹـ‚ٌ‚¾‹Zڈp‚âگفŒvژè–@‚ب‚ا‚ً•ھ‚©‚è‚â‚·‚‰ًگà‚µ‚ؤ‚¢‚پB HDMI 2.0‚ج‚إ‚«‚邱‚ئ

HDMI 2.0‚ج‚إ‚«‚邱‚ئ

‰f‘œ/‰¹گ؛‚ج“`‘—‹Kٹi‚ئ‚µ‚ؤ’è’…‚µ‚½HDMI‚جچإگV‹KٹiپuHDMIƒoپ[ƒWƒ‡ƒ“2.0پvپiˆب‰؛پAHDMI 2.0پj‚ھ‚±‚ج‚ظ‚اچô’肳‚ꂽپB‚±‚±‚إ‚حپA‚±‚ê‚ـ‚إ‚جHDMI‹Kٹiƒoپ[ƒWƒ‡ƒ“‚ئHDMI 2.0‚إ‚ح‚ا‚ج‚و‚¤‚بˆل‚¢‚ھ‚ ‚èپA‚ا‚ٌ‚ب‚±‚ئ‚ھ‚إ‚«‚é‚و‚¤‚ة‚ب‚ء‚½‚ج‚©‚ف‚ؤ‚¢‚پB SLVSƒCƒ“ƒ^ƒtƒFپ[ƒX‚ًFPGA‚إٹˆ—p‚¹‚و

SLVSƒCƒ“ƒ^ƒtƒFپ[ƒX‚ًFPGA‚إٹˆ—p‚¹‚و

SLVS‚حپAƒfپ[ƒ^گMچ†‚ًچ‚‘¬‚©‚آ’لڈء”ï“d—ح‚إ“`‘—‚·‚é—p“r‚ة‚¨‚¢‚ؤپALVDS‚ة‘ض‚ي‚ء‚ؤ—ک—p‚³‚ê‚é‹@‰ï‚ھ‘‰ء‚µ‚ؤ‚¢‚éƒfپ[ƒ^“`‘—‹Kٹi‚إ‚ ‚éپBFPGA‚ةSLVS‚ًژہ‘•‚·‚éڈêچ‡‚ة‚حپALVDS‚ًژہ‘•‚·‚éڈêچ‡‚ئ‚حˆظ‚ب‚邳‚ـ‚´‚ـ‚ب’mŒ©‚ھ•K—v‚ة‚ب‚éپB–{چe‚إ‚حپASLVS‚جٹT—v‚ئپAFPGA‚ة‚¨‚¯‚鉗p—ل‚ًڈذ‰î‚·‚éپB ’·‹——£چ‚‘¬“`‘—‚ھ‰آ”\پALVDSƒCƒ“ƒ^ƒtƒFپ[ƒX“‹چع‚جLEDƒhƒ‰ƒCƒo

’·‹——£چ‚‘¬“`‘—‚ھ‰آ”\پALVDSƒCƒ“ƒ^ƒtƒFپ[ƒX“‹چع‚جLEDƒhƒ‰ƒCƒo

ƒUƒCƒ“ƒGƒŒƒNƒgƒچƒjƒNƒX‚حپALVDSƒCƒ“ƒ^ƒtƒFپ[ƒX‚ً“‹چع‚µ‚½LEDƒhƒ‰ƒCƒoپuTHL3512پvپuTHL3514پv‚ً”•\‚µ‚½پBLVDSƒVƒٹƒAƒ‹ƒCƒ“ƒ^ƒtƒFپ[ƒX‚ً—p‚¢‚½گ§Œن‚ة‚و‚èپAچ‚‘¬پE’·‹——£“`‘—‚ئچ‚ƒmƒCƒY‘دگ«‚ً‰آ”\‚ة‚µ‚½پB ƒCƒ“ƒ^پ[ƒtƒFپ[ƒXICٹˆ—p‚جƒXƒXƒپ

ƒCƒ“ƒ^پ[ƒtƒFپ[ƒXICٹˆ—p‚جƒXƒXƒپ

ƒچƒWƒbƒNIC‚ج“dŒ¹“dˆ³‚ج’ل‰؛‚ة”؛‚¢پAƒCƒ“ƒ^پ[ƒtƒFپ[ƒXIC‚جڈd—vگ«‚ھ‘‚µ‚ؤ‚«‚½پBŒ»چف‚إ‚حپA’P‚ب‚镉‰×‹ى“®‚جژè’i‚إ‚ح‚ب‚پA‚و‚èŒّ—¦‚ھ—ا‚پA‚و‚èˆہ‘S‚بگMچ†“`‘—‚جژè’i‚ئ‚µ‚ؤ‚»‚ج‰؟’l‚حچ‚‚ـ‚ء‚ؤ‚«‚ؤ‚¢‚éپB–{چe‚إ‚حپA‚ـ‚¸ƒCƒ“ƒ^پ[ƒtƒFپ[ƒX‰ٌکH‚جٹî–{‚ًچؤٹm”F‚µ‚½ڈم‚إپAٹeژيƒCƒ“ƒ^پ[ƒtƒFپ[ƒXIC‚ج‰ت‚½‚·–ًٹ„‚âچإگV‚جگ»•i“®Œü‚ًڈذ‰î‚·‚éپB