A-Dコンバーターの「ノイズ・スペクトル密度」を理解する:NSDとは何か(5/5 ページ)

信号アクイジションシステムについては、数十年にわたってより広い帯域幅が求められる状況が続いています。その結果、高速A-Dコンバーター(ADC)で最も重視される性能項目にも緩やかな変化が生じています。それに伴い、ADCの性能は、従来とは異なる方法で測定されるようになってきました。

システムでADCのNSDに影響を及ぼす要素

高速ADCの性能を低下させる外部要因は数多く存在します。それらによってS/N比は低下し、ノイズ密度は高くなります。ADCのSNRFSやサンプルレートに影響を及ぼす要素は、いずれもシステムにおいてNSDに影響を及ぼす可能性があります。ここでは、サンプルレートの高いADCのS/N比を低下させる要因となるクロックジッタに注目することにします。

高速、高分解能のADCでは、入力されるクロックの質に依存して性能が変動することがあります。高速ADCにおいて高いS/N比を得るには、アプリケーションの入力周波数の要件に基づいて、クロックのRMSジッタについて慎重に検討しなければなりません。性能の高いADCがあったとしても、クロックのRMSジッタによって高い入力周波数でノイズ性能が劣化し、S/N比が低下してしまうことがあります。それによってADCのNSDが変化することはありませんが、ジッタの大きいクロックはシステムのS/N比を制限してしまうのです。

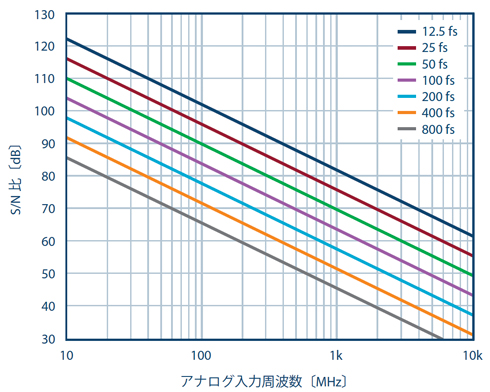

同じクロックのRMSジッタによってADCのアナログ入力周波数が3倍になり、S/N比の最高値は10dB低下します。所定の入力周波数fAにおいてアパーチャジッタtJのみによって生じるS/N比の低下は、次式によって求められます。

図6は、クロックジッタがS/N比に及ぼす影響を示したものです。アナログ入力周波数を変化させた場合に、大きさの異なるクロックジッタによってS/N比にどのような影響が及ぶのかを示しています。クロックジッタは、フェムト秒の単位で変化させています。高い入力周波数に対しても、低い入力周波数で得られるのと同じS/N比を実現するには、クロックのRMSジッタを抑える必要があります。例えば、クロックのRMSジッタが200フェムト秒である場合、ADCのS/N比は、入力周波数が250MHzの時に70dB未満に制限されます。一方、1GHzの入力信号に対して同じ70dBのS/N比を得るには、クロックのRMSジッタを50フェムト秒に抑える必要があります。

ADCのNSDは、フルスケールの信号パワーから、1Hzを単位とする帯域全体に広がったノイズパワーを差し引いた値として簡単に定義できます。FFTで処理するサンプル数を変えても、ADCのNSDは変わりません。周波数帯域全体にノイズが拡散されるだけです。

ノイズシェーピングの特性は、ADCのアーキテクチャと、帯域外のノイズをデジタルフィルターによって処理するか否かによって異なります。システムで必要とする帯域よりもかなり広い帯域幅を持つナイキストレートのADCがあったとします。その場合、処理利得によって、対象とする帯域内のダイナミックレンジが向上します。

著者プロフィール

Ian Beavers氏[Ian.Beavers@analog.com]

Ian Beavers氏は、Analog Devices(ノースカロライナ州グリーンズボロ)のオートメーション/エネルギー/センサー・チームのプロダクト・エンジニアリング・マネージャです。1999年、アナログ・デバイセズ入社。半導体業界での経験は19年以上。ノースカロライナ州立大学で電気工学の学士号を、グリーンズボロのノースカロライナ大学でM.B.A.を取得。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

A-D性能の理論と現実

A-D性能の理論と現実

16ビットA-Dコンバータの理論S/N比は98.08dB。しかし、一般的な16ビットSAR(逐次比較)型A-Dコンバータのデータシートを見ると、S/N比は84〜95dBとなっていることが多い。95dBが98.08dBよりも悪い値であることは確かなのだが、この差をどう理解すればよいのだろうか? 理論値と現実のスペックの関係性について考える。 FFTによるA-Dコンバータの評価

FFTによるA-Dコンバータの評価

移動平均の力:デジタルフィルタ

移動平均の力:デジタルフィルタ

A-Dコンバータを使用する際には、コンバータからのいくつかのサンプル出力に対して、コントローラまたはプロセッサを用いて平均化アルゴリズムを適用すると、変換後の信号を滑らかにすることができる。さらにシステムの実効精度を上げられる。 ΔΣ型A-Dコンバータの要点(その2)

ΔΣ型A-Dコンバータの要点(その2)

複雑なA/Dコンバータの回路構成を極める!

複雑なA/Dコンバータの回路構成を極める!

民生機器、計測、通信、自動車、工業機器、医療器など、さまざまな分野に使われて「データ・コンバータ」。今回はA/Dコンバータについて解説する。 SAR vs ΔΣ どちらのA-Dコンバータを選ぶか

SAR vs ΔΣ どちらのA-Dコンバータを選ぶか

デルタシグマ(ΔΣ)型A-Dコンバータと、逐次比較レジスタ(SAR)型A-Dコンバータ、どちらのデバイスを選ぶべきかを検討していく。