高速シリアル伝送におけるジッタの種類とその特長:高速シリアル伝送技術講座(10)(4/4 ページ)

前回は高速シリアル伝送で使用されるSerDes(シリアライザ・デシリアライザ)について説明しました。今回はSerDesなどの高速シリアルI/Fで、波形測定の際に観測されるジッタの種類とその特長について説明していきます。

2-2:シンボル間干渉(ISI:Intersymbol Interference)

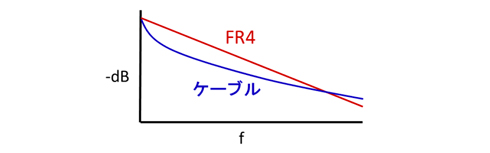

インサーションロス(図7)のある伝送路を信号がトグル(1,0のスイッチング)し通過すると、最大周波数の信号は最も大きく減衰しますが、あるトグル周波数以下の信号では送信端と同じ最大振幅を保ったまま減衰しません。

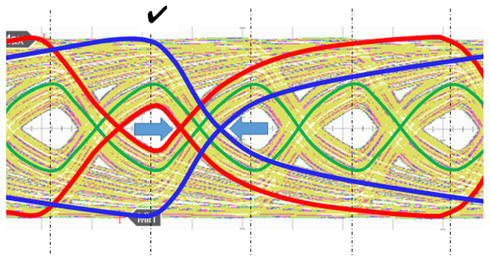

図8はジッタを伴った受信端でのEYE波形です。波形上の青線は最大周波数の6分の1周期の111111000000パターンを繰り返し、受信端での最大振幅は減衰していません。赤線は000001000001もしくは111110111110のデータを繰り返して出力しています。緑線は101010を繰り返して出力しています。

✔印部分での赤線と青線の時間軸でのデータ変化点は同じで、赤青とも同じエッジレートで信号が変化しています。ただし変化の開始する垂直軸方向の位置(電圧)が異なっており、この状態で赤と青の波形を重ねると、図8の矢印で囲まれた時間軸でのタイミングが大きくずれていることが分かります。

デジタルのシリアル通信ではデータの内容に依存して低い周波数から高い周波数を含み、一定の時間間隔でスイッチングしていますが、インサーションロスのある伝送路を通過すると、減衰した高周波成分の信号(赤)は低周波振幅の大きな信号(青)と重ね合わせると遷移開始の電圧が異なるため、ISIジッタが発生しEYEの開口は小さくなります。

このようなインサーションロスのある伝送路で、トグル周波数の異なる信号を流した場合に発生するジッタがISIジッタです(DC結合または完全にDCバランスが取れているデータでのAC結合で、受信端での最大トグル周波数の信号振幅が出力端と同じ場合やクロックの様な単一周波数ではISIジッタは発生しません)。

この伝送路の帯域不足によるISIジッタはアナログのCTLE(Continuous Time Linear Equalizer)、デジタルのFFE(Feed Forward Equalizer)/DFE(Decision Feedback Equalizer)で補償の対象となるジッタです。

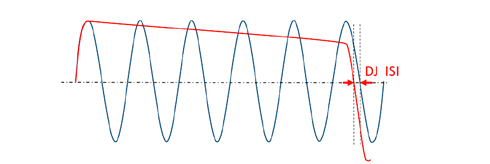

あまり意識されていませんが、ACカップリングでコンデンサの容量が小さいと、図9のようにランレングスの長い(1や0の連続)シリアルコーディングでは、固定値が長く続くために電圧降下が起こり、ここでもISIジッタが発生します(DCバランスが正しく取れていないコーディングでのコンデンサー充放電のアンバランスも同様です)。

また伝送路の特定部分で発生するインピーダンスミスマッチの信号反射が、受信端での波形遷移点に重なることでもISIジッタは発生します。

これらのISIジッタは半導体のCTLEイコライザーでは補償できないため、以前に説明したシリアルコーディングの選択や伝送路のインピーダンス管理が重要になります。

3:有限非相関ジッタ(BUJ:Bounded Uncorrelated Jitter)

隣接信号線からのクロストークなどでデータとの相関関係のないPeak to Peakで表現できるジッタです。ランダム性のあるジッタですが最大値を持つDJの一つで、ランダムジッタとは異なるため分離する必要があります。

以上が高速シリアル伝送で観測されるジッタの種類とその特長です。これらのジッタ特性を把握し、デバイスや伝送路での挙動を理解することで、よりシグナルインテグリティを向上させた設計が可能になります。

特に境界のないランダムジッタについては、デジタル系エンジニアには理解しづらいパラメータの一つですが、自然界の一般的なばらつき現象として、最大値を数値化して対応していることを理解できたのではないでしょうか?

【参考文献】

・ギガビット伝送システム開発力強化集中講座 CQエレクトロニクスセミナ2012 講演資料 河西基文.

・ナショナルセミコンダクタージャパン株式会社 LVDSオーナーズマニュアル 第3版/第4版

・Fibre Channel -Methodologies for Jitter and Signal Quality Specification-MJSQ Working Draft T11.2 / Project 1316-DT/ Rev 14

筆者Profile

河西基文(かわにし もとふみ)/ザインエレクトロニクス シニアエキスパート

ナショナルセミコンダクタージャパンやジェナムジャパンなど、25年にわたり高速通信系半導体の製品開発・サポートおよびマーケットの開拓に従事。伝送路を含んだ半導体の高速設計手法が確立されていない時代に、LVDSオーナーズマニュアルの作成など、同マーケットの成長・普及に寄与してきた。

現在は日本のSerDes製品開発の先駆者的存在のザインエレクトロニクスで、プロダクトマーケティング・開発支援や人材育成などを行っている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

高速インタフェースで使用されるSerDes 〜 種類と特長、その歴史

高速インタフェースで使用されるSerDes 〜 種類と特長、その歴史

代表的な3種類のシリアライザ(Serializer)とデシリアライザ(De-serializer)の機能と歴史について説明していきます。 差動伝送路のケーブル・コネクターの選び方と設計上の注意

差動伝送路のケーブル・コネクターの選び方と設計上の注意

基板間や筺体間の通信に使用されるケーブルとコネクターに求められる特性やその選定方法、ピンアサインなどについて説明していきます。 LVDS PHY製品と伝送路の設計(その1)

LVDS PHY製品と伝送路の設計(その1)

LVDS PHY(物理層)製品を使用する上で必要な一般的な知識とともに、伝送路の設計方法について詳しく解説していきます。 終端方式と高速シリアルI/Fデバイス

終端方式と高速シリアルI/Fデバイス

今回は、LVDS、CML/PECL、計測器などの終端方法と、シリアル伝送デバイスの種類について解説します。 接続形態(トポロジ)と特性インピーダンス

接続形態(トポロジ)と特性インピーダンス

今回は接続形態(トポロジ)、特性インピーダンスについてです。LVDS系テクノロジーのさまざまなトポロジとその基本な構成、またPECLやCMLを使用して同機能を高速で実現する方法などについて紹介します。 高速伝送の代表的な物理層 LVDS・PECL・CML

高速伝送の代表的な物理層 LVDS・PECL・CML

今回は、高速差動伝送で使用されている代表的な物理層である「LVDS」「PECL」「CML」の特長、接続方法、用途例を紹介していきます。 差動信号伝送のメリット ――使用されている技術と注意点

差動信号伝送のメリット ――使用されている技術と注意点

高速シリアル伝送技術について基礎から学ぶ本連載。2回目は、差動信号伝送の特徴、メリットに焦点を当て、使用されている技術や注意点について解説していきます。