半導体(4) ―― 実際に経験した不良と対策(III):中堅技術者に贈る電子部品“徹底”活用講座(63)(2/2 ページ)

前回に引き続き、筆者が実際に半導体を使用する中で経験した思いがけない不良や原因が解明できていない不良について説明していく。

特定条件下のアバランシェ耐量低下

パワーMOSFETにおいて希有な不良メカニズムに遭遇した事例です。

前回説明した『チップ無断変更』の海外メーカー製2チップパワーICにおいてMOSFETの焼損事故が再発しました。

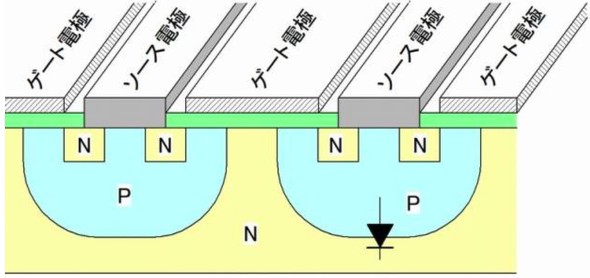

図3にこのMOSFETに用いられる2重拡散型のMOSFETの断面図を示します。この種のMOSFETには通常、アバランシェ耐量というTVS(Transient Voltage Suppressor)と同様なサージ耐量があります。この不良は通常のアバランシェ耐量試験では差異は見つからなかったものの、市場で1%近い故障を起こした事例です。

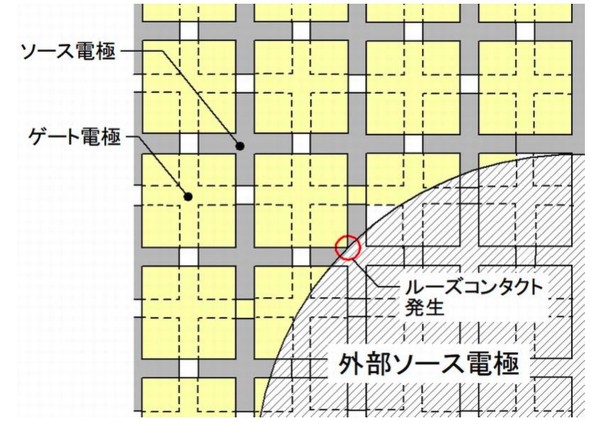

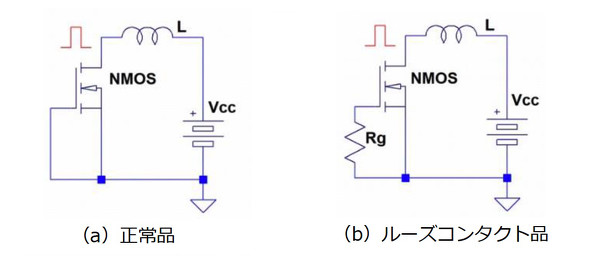

2重拡散型MOSFETのチップ上面は図4に示すように各セルが交互に並んだイメージになっています。そしてチップ全面に設けられたセルの上に半円形のソース電極ボンディング用アルミパッドが設けられ、このアルミパッドによって図5(a)に示すようにセルのゲートとソースが短絡されています。この短絡により該当セルは図3の寄生ダイオードのみがダイードとして動作します。また短絡されるセルのゲートは通常のチップ内ゲートランナー(配線)から切り離されて影響が及ばないようになっています。

【ルーズコンタクトの発生】

6カ月にわたる解析と追跡調査により焼損事故品にはMOSFETのロット依存性があることが分かりました。この事実に基づいて市場で故障したMOSFETと同一ロット品を詳細に観察すると図4に示すように一部のゲート電極がソース電極と辛うじて接触(ルーズコンタクト)するデザインになっていることが観察できました。

この形状では拡散のバラツキによってはゲート電極がソース電極と切り離されて図5(b)に示すゲートオプンに近い構成になり、意図した動作にはならないセルができてしまいます。

この結果、特定の使用条件下においてアバランシェ耐量がなくなり市場で故障したものと分かりました。

【対策】

- 拡散条件のバラツキを考慮して確実に接触が取れるようにソース電極のデザインを変更しました。

- 特定の条件を模擬したアバランシェ耐量の検査回路を作成し全数検査を実施するようにしました。

- パワーMOSFET新規採用時の評価項目に今回の使用条件を一般化して追加しました。

- 特定条件下でアバランシェ耐量低下がなぜ発生するかの真因が分かるまで当該メーカー製品の新規採用を見合わせました。

【品質管理体制の課題】

- 名の通った老舗海外メーカーでしたが品質問題については日本法人の裁量権がなく、海外本社のコントロール下において報告が行われたために技術的に満足する回答がタイムリーに得られませんでした。

- なぜソースパッド電極がこのような形状になっているかの理由はメーカー側(海外本社)の追跡調査では設計年次が古く、担当者や資料も残っておらず不可能とのことでした。しかし半導体メーカーに開発資料がないとの内容は、にわかには信じられるものではありません。

- 先方の内部技術メモにも図4のソースパッド形状の不安定さが記載されていることを指摘するまで当方の指摘(ソースパッド形状の不安定さ)を認めない姿勢は納得できません。

- 営業を含む業界関係者であれば自明の内容でも、英文ハンドブック(原本)の内容を指摘するまで日本語ハンドブックの誤記された値が正規の値だと主張する営業姿勢は納得できません。

(これらの点はこの不良事案を日本法人内で処理したい思いからのようです)

【注】

図5(a)、図5(b)に示すように等価回路が異なるのでアバランシェ耐量が低下することは推測できます。ただ、Rgが存在する図5(b)のルーズコンタクト品がなぜ一般のアバランシェ検査をパスでき、かつ特定の条件下のアバランシェ耐量低下に結びつくのかは推定の域を出ず真因は不明のままです。

なお、この現象は『チップ無断変更』の未承認MOSFETの焼損事故と同じ原因と思われます。ですが上記のようにメカニズムがはっきりしないため根本対策が取れていませんでした。その後、多くのメーカーのMOSFETを同じ回路に使用しましたが問題を起こした事例はなく、当該メーカー製MOSFETの固有プロセスやデザインルールに関係していたのかもしれません。

執筆者プロフィール

加藤 博二(かとう ひろじ)

1951年生まれ。1972年に松下電器産業(現パナソニック)に入社し、電子部品の市場品質担当を経た後、電源装置の開発・設計業務を担当。1979年からSPICEを独力で習得し、後日その経験を生かして、SPICE、有限要素法、熱流体解析ツールなどの数値解析ツールを活用した電源装置の設計手法の開発・導入に従事した。現在は、CAEコンサルタントSifoenのプロジェクト代表として、NPO法人「CAE懇話会」の解析塾のSPICEコースを担当するとともに、Webサイト「Sifoen」において、在職中の経験を基に、電子部品の構造とその使用方法、SPICE用モデルのモデリング手法、電源装置の設計手法、熱設計入門、有限要素法のキーポイントなどを、“分かって設計する”シリーズとして公開している。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

共振子(1) ―― 水晶デバイスとは

共振子(1) ―― 水晶デバイスとは

今回からはマイコンや各種発振器、フィルターに使われる共振子について説明していきます。これらの共振子は回路的には完成度が高く、指定された使い方を間違えなければ正しく動作します。発振器として市販されている部品もありますので適材適所で使い分けることが肝心になります。 電気二重層キャパシター(4) ―― 主な特性と使用上の注意点、寿命計算

電気二重層キャパシター(4) ―― 主な特性と使用上の注意点、寿命計算

今回はEDLCにおいて重要視される特性や注意事項、寿命計算の考え方について説明をしたいと思います。 電気二重層キャパシター(1) ―― 概要と原理

電気二重層キャパシター(1) ―― 概要と原理

今回からはキャパシターの一種である電気二重層キャパシター(EDLC)について説明していきます。EDLCは、耐圧は低い(数ボルト以下)のですがその容量はファラド(F)単位になり、大容量と言われるアルミ電解コンデンサーの数百倍から数千倍のエネルギー密度になります。 セラミックキャパシター(6) ―― 新しい構造

セラミックキャパシター(6) ―― 新しい構造

過去2回にわたってセラミックキャパシターの温度特性について説明してきました。今回は最近のセラミックキャパシターに用いられる新しい構造について説明したいと思います。 セラミックキャパシター(5) ―― 高誘電率系キャパシターの温度特性

セラミックキャパシター(5) ―― 高誘電率系キャパシターの温度特性

高誘電率系のキャパシターの温度特性について説明します。この種のキャパシターの温度特性は数式で変化の様子を表すことができません。したがって図表や文章での説明が主体になります。 セラミックキャパシター(4) ―― 温度特性

セラミックキャパシター(4) ―― 温度特性

セラミックキャパシターの温度特性について説明をしていきます。なお、今回、取り上げる温度特性はIEC規格クラス1やその日本版であるJIS規格のクラス1です。