第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編):FPGA Insights

システム設計において、必要な全ての回路をSoCやASICに集積できるとは限らない。このようなときに有用な半導体チップがCPLD(Complex PLD)である。CPLDは低価格化、低消費電力化、高性能化がさらに進んだことで、活用できる範囲も広がった。本稿では、最新のCPLDを中心に、その特徴や産業分野における主な用途について述べる。

設計途中の仕様変更にも柔軟に対応

CPLDは1980年代半ばに登場した。プログラム可能な論理回路デバイス(PLD:Programmable Logic Device)といえば、近年はさまざまなシステム要求に対応可能なFPGAが一般的となっているが、システム設計において、CPLDを適用するケースも増えている。旧来システムをベースに機能拡張などを行うシステム設計では、これまでの設計資産をできるだけ活用した方が効率的であり、新たに拡張する機能をCPLDで設計し、追加することが得策である。

CPLDとFPGAとの違いなど、CPLDの基本的な情報については、本マイクロサイトでもこれまで取り上げてきた(「こんなに使える!CPLD活用術(前編)」、「こんなに使える!CPLD活用術(後編)」)。本稿は、その基本情報を踏まえて、最新のCPLDとその主な機能に注目した。CPLDの一例として、アルテラの「MAX V」CPLDファミリを取り上げて、その概要や産業機器に向けた応用例を紹介する。

まず、システム設計におけるニーズとCPLDの役割について述べる。システム設計者は、常に市場のニーズを満たす製品を、適正な価格でタイムリーに供給していくことが求められている。特に、開発期間の短縮やコストダウンに対して、設計者へのプレッシャはますます強まる一方である。

では、半導体チップの動向はどうであろうか。先端プロセスを用いた最新のASICやシステムLSIは、システムレベルの大規模な回路をワンチップに集積することができる。その上、高い性能と低消費電力を実現するなど、システム設計者にさまざまなメリットをもたらしている。半面、開発期間の長期化や開発費の増大など、ビジネス面の問題点も表面化してきた。つまり、回路設計のやり直しが多発すると商品戦略はもとより、場合によっては企業経営の致命傷になる可能性もある。

こうした中で、CPLDは設計途中での仕様変更や、新しく登場した規格にも柔軟に対応することが容易なことから、さまざまな用途にその応用が広がっている。特に、商品のモデルチェンジ時にはその効果も大きい。例えば、現行製品に搭載している組み込みマイコンやASSPを流用しつつ、CPLDを追加すればI/O拡張やインタフェース・ブリッジなどを行うことができる。つまり、新たなA-Dコンバータやモータ・コントローラを接続して機能を拡張することも容易となるわけだ。使い慣れた組み込みマイコンをそのまま利用できれば、制御用ソフトウェアを新たに開発したり、大幅に修正したりする必要もない。過去に開発したソフトエア資産を再利用できれば、組み込みシステム開発者はその労力を大幅に軽減することができる。

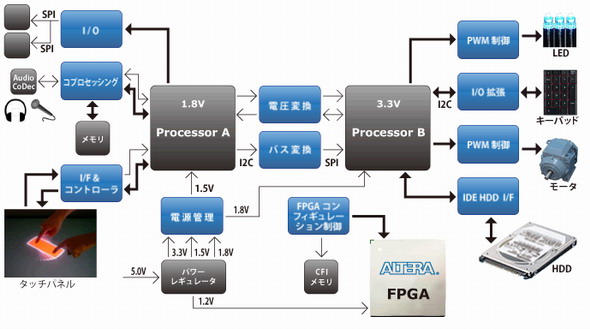

「アナログ制御」や「インタフェース・ブリッジ」などを実現

CPLDの代表的な用途として、5つの事例を挙げることができる。その5つとは「I/O拡張」、「インタフェース・ブリッジ」、「電源管理」、「コンフィギュレーションおよび初期化」、「アナログ制御」である。CPLDではさまざまな機能を実現することができるが、主な機能を図1に示す。

ここでは、アルテラのCPLD「MAX® V CPLD」を一例として、最新のCPLDが備える機能や性能を紹介する。MAX V CPLDは、性能の向上に加えて低価格で低消費電力という特徴を備えている。特に、これまで外部に接続していたフラッシュ・メモリやRAM、オシレータ、PLL(Phase-Locked Loop)といったコンポーネントを集積することができる。このように周辺の機能まで1つのCPLDに統合することによって、システム全体のコストを削減することが可能となる。

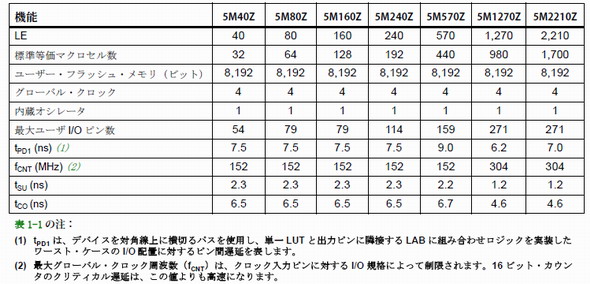

また、消費電力の低減も図っている。チップのコア電源は1.8V単一で、待機時の消費電流は25μAと低く、MAX V CPLDと同等の集積度を持つ他のCPLDに比べて、消費電力を約半分に抑えることを可能とした。これによって、電池駆動の機器でも、1回の充電で使用時間をより長くすることができる。このほか、I/Oインタフェースは1.2V、1.5V、1.8V、2.5Vおよび3.3Vの電圧レベルをサポートしている。MAX V CPLDファミリの機能を表1に示す。

組み込みシステムにおいては、サポートされるパッケージのサイズも重要だ。新たなチップを追加して機能を拡張したために、機器の形状が大きくなったり、重くなったり、コストがアップしたりすることはできる限り避けたいからだ。MAX V CPLDでは、64ピンのMBGA(Micro FineLine BGA)や324ピンのFBGA(FineLine BGA)などを提供している。また、同一パッケージにおけるバーティカル・マイグレーションをサポートしている。

なお、CPLDに関する設計情報を掲載したアルテラのWebページ「はじめてのCPLD設計」では、CPLDが利用される用途などを考慮しつつ、事例を挙げて分かりやすく解説している。CPLDを有効活用するためのさまざまなヒントを見つけ出すことができるかもしれない。

関連情報

●低コスト・低消費電力CPLDによる5つの主要コントロール・パス・アプリケーションの実装

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.