第35回 こんなに使える!CPLD活用術(後編):FPGA Insights

「プログラム可能な論理回路デバイス」というと、FPGAを思い浮かべる読者が多いかもしれないが、他にもCPLD(Complex PLD)があることをご存じだろうか? CPLDを理解してもらうために、前編ではその特徴やCPLDで実現できる機能の概要などについて紹介した。後編では、CPLDの代表的な用途について、より詳しく解説する。

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

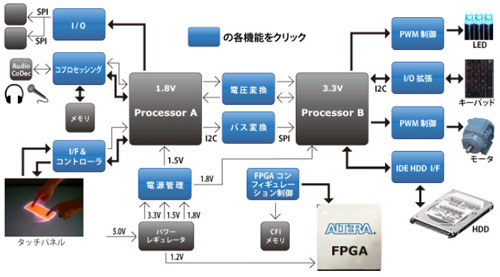

CPLDは1980年代半ばに登場した。フィールドプログラマブルなチップとしての革新性は、その後も回路設計者に大きなインパクトを与え続け、電子回路設計においてCPLDの用途もすそ野が広がっている。その大きな理由の1つは、図1に示すように、CPLDがさまざまな機能を実現することができるデバイスであるからだ。本稿では、アルテラのCPLD「MAX® V 」を1つの例として、CPLDの代表的な5つの用途について、その事例を紹介する。前編でも一部触れたが、その5つとは、「I/O拡張」、「インタフェース・ブリッジ」、「電源管理」、「コンフィギュレーションおよび初期化」、「アナログ制御」である。

シリアル・バスを介してI/O拡張

ある機能に特化した処理を実行させるための標準的な専用ICがASSPである。無駄な回路などを省いた設計となっているため、同等機能のカスタム品に比べて価格は安く、納期も短いなどの特徴がある。このため、仕様が固まった制御に適しており、さまざまな用途で使われている。

しかし、電子機器のモデルチェンジなどに合わせて、機能の拡張や新機能を追加しようとするときに、これまで使ってきたASSPやMCUがそのままでは対応できないこともある。その理由の1つがI/O端子数の不足である。ASSPや組み込みマイコン(MCU)は、I/O端子の数がコストに大きく影響する。このため、回路設計者は、設計の初期段階で必要最小限のI/O端子数を備えたASSPやMCUを選択するのが一般的である。かといってモデルチェンジごとにASSPを再設計したり、I/O数の多いMCUに置き換えたりすると、開発期間や開発コストの問題が新たに生じてくる。

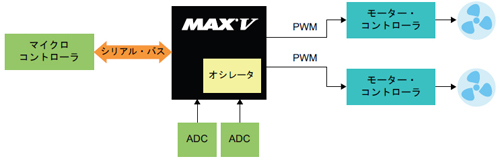

このような課題を解決するのが低コストのCPLDである。MCUとアルテラのMAX Vを、2線式のシリアル・バスで接続することで、I/O端子数を拡張した事例を図2に示す。この例では、既存のMCUを再利用しつつ、MAX Vを介して外部のモータ・コントローラやA-D/D-Aコンバータと接続している。インテルが2010年11月に発表した「インテル○RAtomTME600Cプロセッサー・シリーズ」も、I/O拡張にFPGAを使った製品の一例である。E600Cプロセッサー・シリーズは、インテルAtomプロセッサーとアルテラFPGAのベアチップ同士をPCI Expressで接続し、ワンパッケージにしたもので、システム要件に基づきFPGA側でI/Oを拡張することができる柔軟性を備えている。

インタフェース・ブリッジ

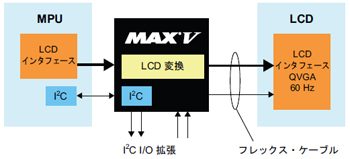

回路基板上には、さまざまな仕様のICや電子部品が実装されている。このためIC間を接続するときに、5Vあるいは3.3Vなど、それぞれのICで入出力信号の電圧レベルが異なる場合がある。また、接続するためのバス仕様もさまざまで、プロトコルあるいはシリアル/パラレルなどの変換が必要となることも少なくない。図3に、MAX Vを使って、低コスト・低消費電力のLCDコントローラとインタフェースをLCDディスプレイに実装する方法の一例を示す。

電源管理

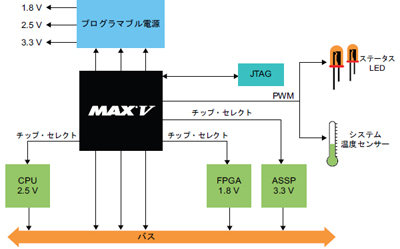

複数の電源電圧を要するICや入出力信号の電圧レベルが異なるICが増加すると、回路基板上にさまざまな電源系統が混在し、電源の管理もそれだけ複雑となってくる。電源管理タスクとしては、多電圧システムの「電源投入」、「システム・リセット」、「チップ・セレクト生成」、「リアルタイム監視」などを挙げることができる。MAX Vでは、自チップを50ms以内に立ち上げた後に、他のICチップを立ち上げるシーケンスを管理する「インスタント・オン」機能や、設計者が3.3V/2.5V/1.8Vなど最適なI/O電圧を選択できる「MultiVolt」機能、各種のパワー・プレーンや関連する電源などのステータスを定期的に監視するために用いる「オシレ―タ」などを実装することができる。一例として、MAX Vによる代表的な電源管理の回路ブロックを図4に示す。

コンフィギュレーションおよび初期化

FPGAやDSPチップ、ASSP、ASIC、フラッシュメモリなどは、コンフィギュレーションや初期化が必要となるICチップである。これらのICチップのコンフィギュレーションや初期化の用途にCPLDを用いることができる。

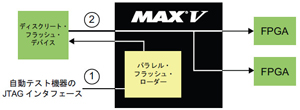

特にMAX Vは、コンフィギュレーションのプログラミングを簡素化するために、パラレル・フラッシュ・ローダーIPを提供している。MAX Vではまず、CPLDのJTAGピンを介して、フラッシュメモリをコンフィギュレーションする。JTAGに準拠していないフラッシュメモリも、パラレル・フラッシュ・ローダーIPを使ってコンフィギュレーションすることができる。次にこのフラッシュメモリを使って、1個またはそれ以上のFPGAをコンフィギュレーションすることが可能である。MAX Vによるコンフィギュレーションのステップを図5に示す。

PWM機能でアナログ回路を制御

MAX Vは、パルス幅変調(PWM)インタフェースを介して、さまざまなアナログ製品と直接接続することができる。CPLDに内蔵したPWM機能により、外部に接続された標準的なアナログデバイス(照明、音声、モーターなど)を、D/Aコンバータなしでもデジタル制御することができる。現在、このような制御は一般的にマイコンで行われているケースが多い。それは、「CPLDが高価で使いづらい」といったイメージが設計者の中にあることや、これまでマイコンのみでも対応することができていたためでもある。MAX Vは、このような設計者のイメージを払しょくすることのできるCPLDである。

CPLD設計のヒントがここにある

なお、CPLDに関する設計情報を掲載したアルテラのウェブページ「はじめてのCPLD設計」では、CPLDが利用される用途などを考慮しつつ、CPLDによるコプロセッシング機能やシステムの電源管理機能などを実現するための事例を、よりわかりやすく解説している。CPLDに関するアプリケーション・ノートやデザイン・サンプルなどの技術資料をダウンロードできる上、デザイン・サンプルの実装方法などもビデオ映像で確認することができる。CPLDの採用を検討している設計者は、CPLDを有効活用するためのヒントをつかむためにも、同サイトを利用してみたらどうだろうか。

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

●低コスト・低消費電力 CPLD による5 つの主要コントロール・パス・アプリケーションの実装

●ゼロ・パワー CPLD を使用したポータブル・アプリケーションにおけるトータル・システム・コストの削減

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2014年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.