最近、「SoC(エスオーシー)」、または、「システムLSI(システムエルエスアイ)」という用語を半導体関連の新聞記事やWebニュースなどで目にすることが少なくありません。例えば、国内半導体メーカーのSoC事業の統合がごく最近は話題になっています。今回はSoCとシステムLSIを解説しましょう。

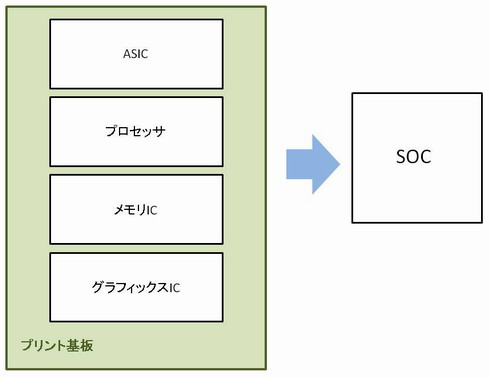

「SoC」は「system on a chip」の略号です。システムをワンチップ(あるいは1枚のシリコンダイ)に集積したもの、という意味です。「システムLSI」はシステムを1個のLSIに集積したもので、ほぼ同じ意味で使われています。ただし「システムLSI」だと1枚のシリコンダイに集積したものとは限りません。この違いについては後述します。

SoCは、1980年代に登場した「ASIC(エイシック)」の後継となる製品だと言われています。ASICとはセミカスタムICの一種で、半導体メーカーがあらかじめ基本的な回路セルを作り込んだウェハー(「マスタースライス」と呼ぶ)をベースに、主に配線工程によって半導体ユーザーが設計した回路を形成する半導体製品です。ちなみにASICとは「application specific integrated circuits」の略号です。

1980年代半ばに登場したASICは、ユーザーが設計したロジックを搭載するシリコンダイでした。その後、1枚のシリコンダイに集積できるロジックの規模(論理ゲート数)が急速に増えていったことにより、それまでは別々のシリコンダイに分かれていたCPUやメモリ(SRAMとROM)、インタフェース、クロック、PLL、グラフィックス、コーデックといった回路も、1枚のシリコンダイにまとめて集積できるようになっていきます。

こうなるとシリコンダイの内容と付加価値が違いますので、従来のASICという表現は的確ではなくなり、半導体メーカーとしては新しい呼称を必要とするようになりました。その中で生まれてきたのが「SoC」であり、「システムLSI」です。

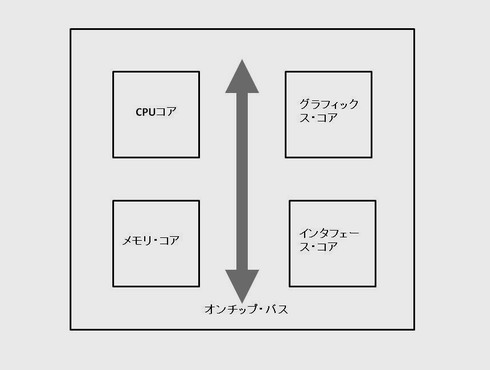

SoCは、「コア」と呼ばれるいくつもの回路ブロックを内蔵しています。プロセッサ・コア、グラフィックス・コア、コーデック・コア、メモリ・コア、インタフェース・コアなどです。コア間は「オンチップ・バス」と呼ぶバスで接続されており、バスを介して信号をやりとりします。

SoCとASICが違うのは、ASICが主にカスタムICを意味していたのに対し、SoCにはカスタムICと標準ICがあることです。標準ICは「ASSP(エーエスエスピー:特定用途向け標準製品)」と呼ばれています。ASSPはあらかじめ仕様が決まっており、データ・シートやカタログなどを半導体ユーザーがあらかじめ入手できます。SoCは登場したころはASICの発展形でカスタムICが主流だったのですが、現在ではSoCのほとんどは標準IC、すなわちASSPになっています。なおASSPは「application specific standard products」の略号です。

SoCとSiP

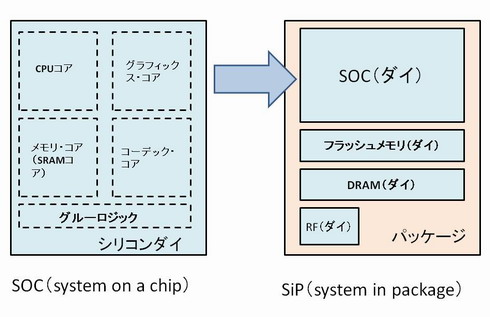

SoCのシリコンダイは普通、標準的なCMOSロジックの製造技術で作られています。しかし半導体ICの中には、独自の製造技術を使っており、標準的なCMOSロジックの製造技術だけでは作れないものがあります。独自の製造技術と標準的なCMOS製造技術の両方を使ってシリコンダイを製造することもできるのですが、製造工程のステップ数が大幅に増えて製造コストが増大するという問題があります。また、標準的なCMOS製造技術には組み込みづらい特殊な製造技術も存在します。あるいは、1枚のシリコンダイにまとめるとシリコン面積が大きすぎて製造が困難になってしまう、という場合があります。

そこで1枚のシリコンダイにまとめることはせずに、数枚のシリコンダイを1個のパッケージに収納したのが「SiP(シップ)」です。SiPは「system in package」の略号で、1個のパッケージでシステムを実現した製品、という意味になります。

代表的なSiPの例は、高性能マイクロプロセッサのシリコンダイと大容量DRAMのシリコンダイ、大容量フラッシュメモリのシリコンダイを組み合わせたものです。これらのシリコンダイはいずれもかなり大きく、また製造技術がかなり違います。1個のシリコンダイにまとめてしまうことは現実的ではありません。しかし携帯電話機といったモバイル機器ではプリント基板の面積をなるべく小さくすることが求められます。そこでプロセッサやメモリなどのシリコンダイを別々のパッケージに収納するのではなく、一つのパッケージに収納したSiPが使われています。

SiPの考え方自体は新しいものではありません。1980年代には「マルチチップ・パッケージ(MCP:multi-chip package)」と呼ばれて主にカスタム品として製造されていました。その発展形として現在ではSiPと呼ぶようになっています。SiPもSoCと同様に、現在では標準ICとしてカタログに掲載されていることが少なくありません。ただしカタログにはSiPやSoCなどとは記述していませんので、カタログを一見しただけでは分からないのが普通です。

なお、SoCとSiPは厳密に区別されていますが、システムLSIにはSoCだけでなく、SiPを含めることがあります。システムLSIは、1個のシリコンダイとは限らないのです。

その意味で最近では、シングルダイのパッケージ品とマルチダイのパッケージ品の区別があいまいになっています。過去には「チップ」は「シリコンダイ」と同じ意味であり、チップとパッケージが区別されていました。最近ではパッケージに収納された状態の半導体製品を「チップ」と呼ぶことが多くなっています。こうなると「チップ」が複数のシリコンダイを内蔵することがありますし、実際にそのような標準IC製品が存在しています。

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.