パイプライン型

パイプライン(pipeline)型とは、アナログ信号をデジタル信号に変換するADコンバータを実現する回路手法の1つ。通信機器や映像機器などに搭載されている。

ADコンバータを実現する回路手法の代表的なものとしては、パイプライン型の他、逐次比較(SAR:Successive Approximation Register)やΔΣ(デルタ・シグマ)型、フラッシュ型などがある。いずれの手法も、得意分野と不得意分野を併せ持つ。その中にあって、パイプライン型は不得意の分野が比較的少ない回路手法である。すなわち、数十M〜数百Mサンプル/秒と高いサンプリング速度が得られると同時に、12ビットや14ビット、16ビットといった高い分解能を実現できるからだ。パイプライン型以外は、高い分解能が得られるものはサンプリング速度が低くなり、高いサンプリング速度が得られるものは分解能が低くなる傾向にある。

複数のADコンバータを多段接続

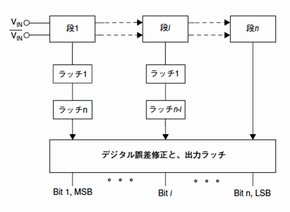

図1 パイプライン型ADコンバータのブロック図

1ビットADコンバータなどから構成されるステージ(段)を複数個使用し、最上位ビット(MSB)から順次決定し、最終的に最下位ビット(LSB)を決めることでデジタル化が完了する。

パイプライン型ADコンバータでは、1ビットや1.5ビットといった分解能が低いADコンバータを複数個用意し、これらを多段接続したパイプライン回路を使ってアナログ信号をデジタル信号に変換する(図1)。

動作原理を簡単に説明しよう。まずは、1ビットADコンバータを使って最上位ビット(MSB:Most Significant Bit)を決める。その後、MSBの値をDAコンバータでアナログ信号に戻し、アナログ入力信号と比較して差を求める。この差を次段の1ビットADコンバータに入力し、MSBから2ビット目の値を決める。この処理を順次実行し、最下位ビット(LSB:Least Significant Bit)を求めるまで繰り返す。こうしてアナログ入力信号をデジタル信号に変換するわけだ。

この手法のメリットは、前述のように高い分解能と高いサンプリング速度を両立できる点にある。しかし、デメリットも存在する。それは、各ビットを順次求める手法を採用しているため、段数とクロックの積に相当する時間だけ出力が遅れてしまうことだ。これをパイプライン遅延、もしくはレイテンシと呼ぶ。さらに、直流(DC)精度については、SAR型やΔΣ型に劣る傾向にあるというデメリットもある。

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2015年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.