半導体の温故知新(6)――MOSトランジスタの次はTFET?:津田建二の技術解説コラム【歴史編】

最先端半導体の世界は今、16nmあるいは14nmのFinFET(フィンフェットと発音)と呼ばれるトランジスタを基本とする集積回路が量産されようとしています。今回は、MOSFETの基本原理に立ち返りながら、今後の集積回路を考察してみます。

最先端半導体の世界は今、16nmあるいは14nmのFinFET(フィンフェットと発音)と呼ばれるトランジスタを基本とする集積回路が量産されようとしています。インテルは、22nmプロセスノードのマイクロプロセッサ「Haswell」の時からFinFETプロセスを使ってきました。なぜ、このトランジスタが注目されるのでしょうか? これまでとは何が違うのでしょうか? また、FinFETの先はどうなるのでしょうか? MOSFETの基本原理に立ち返って、今後の集積回路を考察してみます。

MOSFETの基本原理

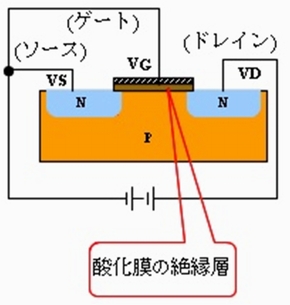

MOSFET(図1)の特長は、何といっても集積しやすさにあります。最初のトランジスタはnpnあるいはpnpのバイポーラトランジスタでした。バイポーラはその構造上縦方向にコレクタ、ベース、エミッタが形成されており、一番下にあるコレクタ、真ん中のベース、表面のエミッタの全ての端子電極を、シリコン表面から採るために余分な面積を必要としていました。これに対してMOSトランジスタはドレイン、ゲート、ソース全て表面に形成されていますので、余分な面積を設けることなく端子電極を取り出せました。限られた面積のシリコン表面にトランジスタを数多く形成できました。

開発当初のMOSFETは、ゲート酸化膜の状態によって表面準位と呼ばれる欠陥によるエネルギー準位がバンドギャップ内にできるため、ゲート電圧によって完全に制御できる訳ではありませんでした。しかし、日米の半導体研究者たちが競い合って酸化膜とシリコンの界面を制御できる条件を見いだしたため、ムーアの法則に従ってMOSトランジスタの集積度を上げることができるようになりました。

ムーアの法則で集積度を上げることは、デジタル技術と極めて相性が良かったのです。デジタル技術は基本的に、オン・オフだけの2進法を使います。2進法は桁数がべらぼうに増えていきます。例えば、10進法の数字の9は、2進法では4桁の1001になります。9×9は81ですが、2進法では、1001×1001=1010001となって8桁にもなります。それでも集積度をどんどん上げられるため、トランジスタの数を増やすことが可能になりました。

クロック周波数と熱

ただ、性能(速度)を上げるために、デジタルの基本ロジック回路はpチャンネルMOSFETからより速度の速いnチャンネルMOSFETへと変わりました。しばらくnチャンネルMOSFETの時代が続きましたが、動作している時は必ず電流が流れていました。このため消費電力が大きくなりました。そこで、CMOSロジックを導入して消費電力の増加を食い止めました。CMOSロジックは、オン、オフどちらの状態でも電流は流れません。しかし、オンからオフ、またはその逆の遷移するときに貫通電流が流れます。このため頻繁にオンオフスイッチングをするたびに電流がたくさん流れました。すなわちクロック周波数が高くなるにつれ、消費電力は2乗で増加していきました。

クロック周波数はもはや3GHzくらいから上げることをせず、むしろマルチコアで並列処理動作によって性能を上げるように変わってきました。これ以上クロック周波数を上げると発熱が激しくなってきたからです。

この間、MOSトランジスタの微細化は進んでおり、90nmから65nm、45nmへと微細化されていました。微細化に性能向上も大きく貢献していました。しかし、微細化されるほどMOSトランジスタにとっては短チャンネル効果と呼ばれる、ゲートしきい電圧Vthの低下が顕著になってきました。ゲート長Lが短くなるにつれ、Vthが下がるため、LのバラつきによってVthが大きくバラつく、さらにはしきい電圧よりも電圧を下げてもなかなか電流が下がらないというサブスレッショルド電流の傾きが大きくなる、という問題が顕著に表れるようになってきました。これらの問題は、スリープ時や静止時の消費電流が大きくなってしまいます。

FinFETとFD-SOI

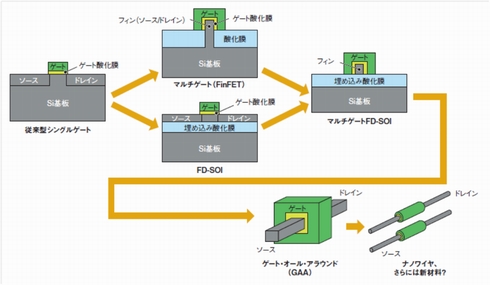

いよいよ、MOSトランジスタの限界かと思われますが、リーク電流を増やしている原因の1つはドレイン空乏層が完全に閉じないことによるので、ゲート電界を3方向から加えて空乏層を完全に閉じさせてリーク電流を食い止めよう、というトランジスタが登場しました。これがFinFETです(図2)。もう1つの解が、FD-SOIです。これは上下のゲートから空乏層をふさいでしまおうという考えで、STマイクロエレクトロニクスやIBMなどが進めています。

図2 従来のMOSFETからFinFET、あるいはFD-SOI技術のFETに選択肢が広がり、やがてFD-SOIのFinFET、さらにはゲートで周囲を囲むゲート・オール・アラウンド構造などの道がある。TFETへの道もある (クリックで拡大) 出典:服部毅著「6-2 半導体微細化・大口径化とプロセス技術」、『メガトレンド半導体2014-2023』、日経BP発行

FinFETは、TSMCをはじめ、サムスン、インテルなどが進めています。特にインテルが採用した22nmノードのマイクロプロセッサでは、その断面が台形に近く、大量生産は期待以上にうまくいきました。しかし、14nmノードではもっとアスペクト比が大きな細長い長方形の断面となり、製造が困難を極めていました。最近ようやく、軌道に乗り始めた所だといわれています。

FinFETは静止時の消費電流は小さくなりますが、動作時は相変わらずです。やはり、マルチコアなどの並列処理アーキテクチャを使って、クロック周波数を上げずに性能を上げるしか手はありません。この先の10nm、7nmなどもFinFETで微細化できるのでしょうか。まだ誰にも分かりませんが、Finの形状がさらに細く長くなると難しくなることは間違いないでしょう。

サブスレッショルド電流は、物理原理に立ち返ると、熱電子がわき出てくるボルツマン分布に従うことで決まるため、この原理を使わないトランジスタを求める声が出てきました。これがトンネルFET(TFET)です。pn接合を使って、ドレインとソースの間にバリアを作っておき、ゲート電圧でそのバリアが薄くなるようにバイアスをかけます。そうすると電子はトンネル現象を使ってソースからドレインへ流れます。電流を流さないサブスレッショルド電流の傾きは従来のMOSFETよりもシャープな傾斜になるという実験結果が得られています。ただし問題は駆動電流がまだ小さいことです。研究は進んでいますので、今後の成果を待ちましょう。

トランジスタ構造を見直す動き

結局、MOSトランジスタが10nmに微細になるにつれ、トランジスタ構造を見直す動きが出てきています。基本的な原理から見直し、もっと簡単でもっと性能が上がり消費電力が下がるトランジスタやゲート回路を創出できると、この壁を突破する新しい「LSI」となるでしょう。若いエンジニアがこれを生み出して社会を変えるようになれば素晴らしいと思います。

Profile

津田建二(つだ けんじ)

現在、フリー技術ジャーナリスト、セミコンポータル編集長。

30数年間、半導体産業をフォローしてきた経験を生かし、ブログや独自記事において半導体産業にさまざまな提言をしている。

提供:ルネサス エレクトロニクス株式会社 / アナログ・デバイセズ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2015年5月31日

Copyright © ITmedia, Inc. All Rights Reserved.