半導体(11)―― MOSFETの新しいアバランシェ検査法:中堅技術者に贈る電子部品“徹底”活用講座(70)(3/3 ページ)

今回は今まで説明してこなかったアバランシェ検査の新しい考え方について説明します。

2次降伏領域の発生(S/B:SecondaryーBreak)

従来、MOSFETの順方向安全動作領域(SOA)にはバイポーラトランジスタのS/B領域に相当する領域はないとされ、SOAの各曲線は熱制限領域のみとされてきました。

しかし近年のMOSFETの微細化にともないバイポーラトランジスタのS/B動作と同等の現象が高電圧領域で見られるようになってきましたが、文献を調査しても微細化とS/Bの関係について簡明に説明したものは入手できませんでした。

S/Bとは

バイポーラトランジスタのS/Bというのは、通常のVCE降伏(1次降伏)に続いて高電圧/大電流域でブレーク電流が増加すると負性抵抗(=電流集中)が発生することを指しています。電流集中が局部的なホットスポットの発生に結びつき、その部分のインピーダンスが低下することで正帰還的に電流集中を招くと考えられています。

MOSFETのS/B

MOSFETにおける電流集中メカニズムは次に説明するようにバイポーラトランジスタとは異なりますが現象の同一性からMOSFETの現象も一般的にはS/Bと呼ばれています。

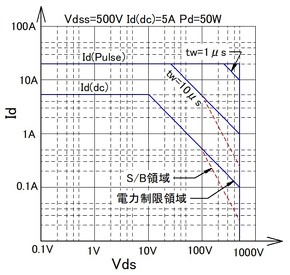

この現象が発生すると図7に示すように高電圧領域で順方向許容電流が著しく制限されます。

MOSFETのS/Bのメカニズムとして以下のような正帰還サイクルによる説明がいくつかの資料で見られます。

1つはMOSFETが持っている微小電流域でのVgs-Id特性の本来の温特が正である影響による説です。Idが微小な領域ではVgs-Idの温度特性が正になることに起因しています。

このS/B現象のその他の説明として次のような資料もあります。

①MOSFETはゲートを順バイアスするとゲート電極直下にチャネルが形成され始め、しきい値電圧Vthを超えるとドレイン電流が流れ出します。このVthの温特は負です。

②FETのオン抵抗(RON)をゲート電圧で制御する(リニア)領域のRONはゲート印加電圧(VGS)とVthの差(VGS-Vth)に反比例します。VGSの温特が負のため(VGS-Vth)が高温で大きくなることでRONは下がります。

③MOSFETの温度が上がるとVthが下がり、RONが下がります。

④RONが下がったチャネルに電流が集中→温度が上がる→Vthが下がります。

⑤Vthが低下→RON低下→これによりさらに電流が集中するという正帰還によって、局部的に素子が破壊し、全体に破壊が広がります。

ただし、この説ではRONの温度特性が正(ΔTch=+100℃でRON約2倍)であることによる電流の自己バランス効果が無視されています。このことを考慮すると④〜⑤の説明に疑問を生じます。加えて上記2つの説では近年のセルサイズの微細化の影響が抜けています。

以下は私見ですが次のように考えています。

- ゲート電極直下にはP層がN反転したチャネルが生成されていますがこのチャネル厚みはP層(0V)とゲートの電位(+)差による電界によって決まります。

- セルサイズが大きい旧来のMOSFETではP層内にほぼ均一に電界が分布していたが、微細化が進みチャネル幅が狭く(=P層の厚みが薄く)なると、相対的に高電位のドレイン(N層)がソースに近づいてきます。

- その結果、ゲート電極による電界とドレインの電位に対応するP層内の空乏層とが干渉してチャネル厚みがテーパー状に変形すると同時にVthを低下させます。

これらの現象によってドレイン電圧が高い領域ではチャネル厚みが温度やゲート電位に対して敏感(高感度)になり上記の②、③が顕著に現れるのではないかと考えています。

注)上記のS/Bの説明はあくまでも順方向バイアス時の説明です。本稿で取り上げているアバランシェブレークの期間中はゲートがオフ(逆バイアス)ですからMOSFETのチャネルは形成されず、上記のメカニズムによるS/Bは起こりません。アバランシェとS/B動作は無関係です。資料によっては両者を混用させるような書き方をしているものもありますので内容をしっかり確認することが重要です。

次回は半導体のチップに外部電極を接続するワイヤーボンドについて基礎的な説明をしたいと思います。

執筆者プロフィール

加藤 博二(かとう ひろじ)

1951年生まれ。1972年に松下電器産業(現パナソニック)に入社し、電子部品の市場品質担当を経た後、電源装置の開発・設計業務を担当。1979年からSPICEを独力で習得し、後日その経験を生かして、SPICE、有限要素法、熱流体解析ツールなどの数値解析ツールを活用した電源装置の設計手法の開発・導入に従事した。現在は、CAEコンサルタントSifoenのプロジェクト代表として、NPO法人「CAE懇話会」の解析塾のSPICEコースを担当するとともに、Webサイト「Sifoen」において、在職中の経験を基に、電子部品の構造とその使用方法、SPICE用モデルのモデリング手法、電源装置の設計手法、熱設計入門、有限要素法のキーポイントなどを、“分かって設計する”シリーズとして公開している。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

半導体(7) ―― MOSFETのゲート駆動回路の注意点(2)

半導体(7) ―― MOSFETのゲート駆動回路の注意点(2)

今回はパワーMOSFETの構造とそれに起因する寄生容量について説明するとともに、引き続きゲート駆動回路を中心にした使い方の注意事項を説明します。前回の記事と併せて読んでいただければ理解も深まると思います。 半導体(1) ―― 半導体の製造工程

半導体(1) ―― 半導体の製造工程

今回からは電子回路に欠かせない半導体について説明します。本シリーズでは半導体の市場不良および、その原因を説明するための製造工程の問題を主眼に説明をしていきます。 共振子(1) ―― 水晶デバイスとは

共振子(1) ―― 水晶デバイスとは

今回からはマイコンや各種発振器、フィルターに使われる共振子について説明していきます。これらの共振子は回路的には完成度が高く、指定された使い方を間違えなければ正しく動作します。発振器として市販されている部品もありますので適材適所で使い分けることが肝心になります。 電気二重層キャパシター(1) ―― 概要と原理

電気二重層キャパシター(1) ―― 概要と原理

今回からはキャパシターの一種である電気二重層キャパシター(EDLC)について説明していきます。EDLCは、耐圧は低い(数ボルト以下)のですがその容量はファラド(F)単位になり、大容量と言われるアルミ電解コンデンサーの数百倍から数千倍のエネルギー密度になります。 サーミスタ(1) ―― NTCサーミスタとPTCサーミスタ

サーミスタ(1) ―― NTCサーミスタとPTCサーミスタ

今回から「サーミスタ」を取り上げます。サーミスタの分類について簡単に説明するとともに、サーミスタを使用した回路動作の概要について解説していきます。第1回は、NTCサーミスタとPTCサーミスタの違いとともに、NTCサーミスタによる突入電流制限回路について考察します。 フェライト(1) ―― 磁性

フェライト(1) ―― 磁性

“電子部品をより正しく使いこなす”をテーマに、これからさまざまな電子部品を取り上げ、電子部品の“より詳しいところ”を紹介していきます。まずは「フェライト」について解説していきます。