第3回 SimulinkモデルからHDLを生成 FPGAにDSP機能を実装する(前編):FPGA Insights

FPGAを用いてDSPベースのシステムを構築するのは容易ではない。設計、統合、検証、機能要件の変更、製造への移行時において、開発計画に予期せぬ遅れが生じることもある。現在では、製品開発サイクルを簡素化し、製品ライフサイクルの中で生じる多くの一般的なボトルネックをなくすためのFPGA開発ツールが存在する。本稿では日本アルテラが提供するFPGA設計ツールを用いて、DSP機能を実装するための設計/検証手法などを前編、後編の2回に分けて紹介する。

Michael Parker 米Altera社

FPGA上で高い性能を持つDSPが実現可能なことは周知の事実である。その半面、高い性能のDSPを実現するための課題もある。その1つはFPGA設計時にDSPアルゴリズムを最適化するという作業が伴うことである。現時点では、アルゴリズムをHDLにポーティングする必要があり、次にRTLの機能シミュレーションが、高レベルのシミュレーションテストベクトルに合致していることを検証しなければならない。その後、タイミング検証の作業を行なう。必要とするクロック速度が速いほど、多段のパイプライン処理と回路の最適化が不可欠となる。タイミングの収束には繰り返しの作業が必要となることが多いため、コンパイルする回数も増える。タイミングが収束した後には、再び機能検証を行わなければならない。複数のチャンネルを同時に処理する必要がある場合は、プロセス全体がさらに複雑となる。制御ロジックとメモリーは、所望のクロック速度に対するタイミングマージンを維持しつつ、データフローの適切な時分割多重化を行う必要があるためだ。チャンネル数、FFTサイズ、フィルタ長、システムのクロック速度といったパラメータの変更が生じた場合は、完成した設計データを更新し、再び検証作業を行わなければならない。

設計と検証プロセスを自動化

今日、この設計と検証のプロセス全体を自動化することにより、抽象度の高いレベルでFPGAの設計を始めることができ、テストベンチ生成が簡素化され、可変チャンネルと最適化された性能(400MHz以上)を実現することが可能となった。クロック速度の変更、チャンネル数の増減、FPGAファミリの変更を、数回のクリック操作と再コンパイルによって行うことができる。これにより、設計の再利用や、最終段階での製品の仕様変更も容易に対応することが可能となる。

設計チームは、開発プロジェクトのスケジュールが限られているため、その他の設計手法を採用する時間はないと考えがちである。よりよい設計および検証手法へ投資することと、設計、統合、検証作業における製品開発の遅れを減少させることとの間には、トレードオフの関係が存在する。設計者の中には新しい設計手法を導入することによって、理論どおりの改善が得られるのだろうか、という疑念を持つ場合も多い。

新しい設計手法が現行の設計フローと互換性を有し、段階的に導入することができれば、新しい設計手法を採用しても、そのリスクは劇的に低下する。つまり、設計の特定部分について、新しい手法で実装および検証を行い、従来のHDL手法によって構築した残りの部分と統合すればいい。段階的かつ体系的に新しい設計手法を導入することによって、そのリスクは軽減される。また、設計チームは、新しい設計フローを採用するための初期コストを明らかに上回る効果が得られる部分にのみ、新しい設計フローを採用することができる。

日本アルテラが提供する設計ツール「DSP Builder」は、米The MathWorks社のSimulinkをベースとしており、抽象度の高い設計と生産性の向上を実現しつつ、従来のHDL手法を併用することによって最適化された性能をも得ることができる。また、Advanced Blocksetと呼ぶDSP Builder用ライブラリも用意した。このライブラリをサポートしたことによって、特に、マルチチャンネル設計で生産性をさらに高めることができる。

Simulinkはブロック図による回路記述のためによく使用されているツールである。Simulinkは、レジスタ、乗算器、加算器などのエレメントを用いて、テキストの図を直感的にグラフィカルに、簡単に再現することができる。図1は、簡単な事例として、DSPの中心的要素である、一般的なFIRフィルタの回路ブロックを示したものである。

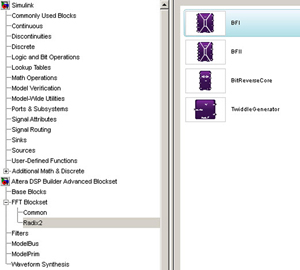

DSPシステムで一般的なもう1つの要素は、FFT(高速フーリエ変換)である。Advanced Blocksetでは、図2のようなバタフライやツイドル要素などの、共通基本ブロックのライブラリを用いて、テキストにあるようなFFT実装を、容易に直感的に構成することができる。

Simulinkの開発環境では、正弦波信号、変調信号、ノイズのような信号など、仮想信号を容易に追加することができる。これにより、テストベンチを生成する作業は、大幅に簡素化される。出力信号は、仮想オシロスコープとスペクトラム・アナライザで終端させて、時間領域応答と周波数領域応答の両方を観測することができるため、FFTまたはFIRフィルタ応答を容易に観測することができる。Advanced Blocksetは、メンターグラフィックスのHDLシミュレータ「ModelSim」と統合することも可能で、Simulinkで設計したデータと、ModelSimを用いて生成されたRTLの出力を容易に比較することができる。これにより、設計者はRTLの出力とSimulink出力が完全に一致することを確認することが可能だ。

公開中(2009年9月〜2010年3月掲載分)

第1回 デジタル信号処理にみる DSPとFPGAの正しい選び方 (前編)

第2回 デジタル信号処理にみるDSPとFPGAの正しい選び方(後編)

第3回 SimulinkモデルからHDLを生成 FPGAにDSP機能を実装する(前編)

第4回 SimulinkモデルからHDLを生成 FPGAにDSP機能を実装する(後編)

第5回 スマートグリッドにおけるFPGAの役割(前編) 新しい「省エネルギー対応」住宅を実現する

第6回 スマートグリッドにおけるFPGAの役割(後編) 新しい「省エネルギー対応」住宅を実現する

関連情報

◎基本を学ぶ「FPGA入門」

FPGAの概要が知りたい、FPGAを試してみたい、と思っている方にFPGAの基本から設計のイロハまで分かりやすく紹介。

◎「テクニカルトレーニング」

FPGAの設計効率をもっと高めたい、最新チップの技術情報を習得したい、という方におすすめ。オンラインでの無料受講も用意。

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.