第49回 こんなところにCPLD――産業用途でみるCPLD活用事例(後編):FPGA Insights

電子回路設計において、CPLD(Complex PLD)の用途が拡大している。ASICなどを用いるのに比べて設計期間を短縮でき、製品の市場投入を迅速に行うことができるからだ。仕様の変更などに対する柔軟性にも優れている。CPLDの特徴をまとめた前編に続き、後編ではCPLDを活用したPWM(パルス幅変調)制御など、産業用途の事例を中心に解説する。

利用シーンに応じてLED輝度を最適化

プログラム可能な論理回路デバイス(PLD:Programmable Logic Device)といえば、FPGAを思い浮かべる読者が多いかもしれないが、回路規模が比較的小さいCPLDで対応可能な用途も多くある。前編でも述べたが、CPLDの代表的な用途として、5つの事例を挙げることができる。その5つとは「I/O拡張」、「インタフェース・ブリッジ」、「電源管理」、「コンフィギュレーションおよび初期化」、「アナログ制御」である。ここでは、アナログ制御やインタフェース・ブリッジ機能などについて解説する。

アナログ回路の制御方式として広く採用されているのがPWMである。パルス波状で出力される信号のデューティー比を変化させることで、平均電圧を可変にする変調方式である。図1にチョッパ制御によるPWMの例を示す。

CPLDにPWM機能を実装することにより、D/Aコンバータなしで標準的なアナログ・デバイス(照明、音声、動作など)をデジタル制御することができる。特に、アルテラのCPLD「MAX® V CPLD」や「MAX® II CPLD」はオシレータを内蔵しているため、外部にオシレータを用意することなく、PWMインタフェースを介してモーター駆動やLEDの輝度、各種センサなどと直接接続し制御することができる。

一例だが、電子機器では電源の状況や無線通信の接続動作などを示すインジケータとして、複数個のLEDを搭載することがある。こうしたLEDの制御回路でも、消費電力を下げるための工夫がいろいろと行われている。例えば、周囲の明るさに応じてLEDの輝度を調節できれば、視認性を犠牲にすることなく、LEDの消費電力を低減することができる。

その一例を紹介する。LEDは、順方向バイアスをかけると発光し、逆方向バイアスをかけた場合に、光センサとして機能するという特性を持つ。そこでCPLDに実装したPWM制御を使って、1個のLEDを「発光素子」と「光量センサ」の2つの機能として使い分ける。これによって周囲が比較的暗い場合は、LEDの輝度をさほど上げなくても視認性を維持することができ、節電につながる。

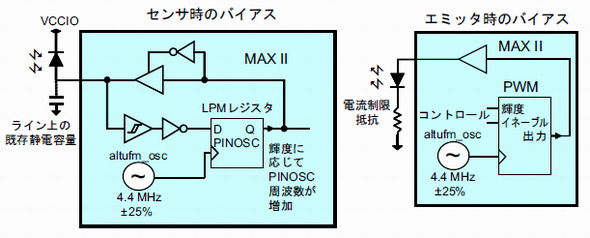

図2にLEDをセンサや発光素子(エミッタ)として使用する場合のバイアス方法を示す。とてもシンプルなフィードバックシステムでLEDの光量を制御することができる。この構成を取ることで、まず周囲の明るさを検知し、LEDをその明るさに適した輝度で発光するように制御する。1つのセンサで、複数のLED輝度を制御することも可能である。

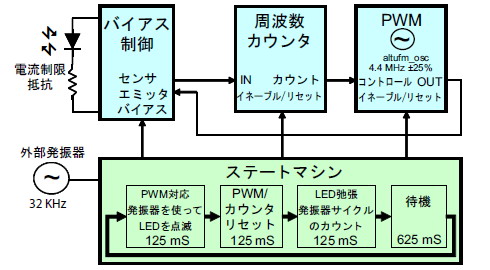

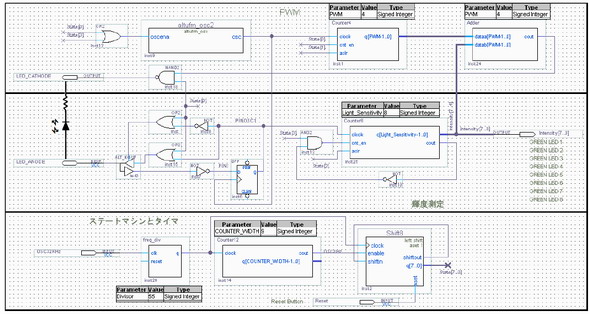

図3に輝度制御機能を組み込んだLED点滅回路の簡略ブロック図を示す。図には示されていないが、LEDの点滅機能を有効にしたり無効にしたりする機能や、点滅する速度を制御したりする機能を追加することも容易に行えるそうだ。

光量の検出と発光は、同一のLEDとオプションのバイアス抵抗を用いて行う。周囲の明るさに基づいてLED輝度を制御すれば、視認性を維持しつつ、LEDに関わる消費電力を約半分にできるという。しかし、LEDの場合はチップごとに発光する特性が異なることがある。このときに、どのような特性のLEDにも適合するよう回路パラメータを素早く設定できるのも、柔軟性に優れたCPLDの強みといえる。

LEDの輝度制御に関して、さらに詳細な情報を入手したい設計者は、アルテラが用意しているホワイト・ペーパー「光量センサ/発光素子としてのLEDを活用」を参照いただきたい。

チップ間を安いコストで接続

CPLDが活用されている用途の1つが、インタフェース・ブリッジの機能である。システムを構成するプリント基板上には、さまざまな機能を備えた複数の半導体チップが実装される。これらのチップは性能や機能の最大化を図るため、独自の電源電圧やバスの仕様を採用するケースが多い。その仕様は今後も多様化し、種類は増える傾向だ。

このときに、チップ間を接続し、システムとして機能させるためのインタフェース機能が必要となる。CPLDを用いれば、互換性のないデバイス間でも、バス・プロトコルや電圧レベルなどの変換を安いコストで実現できる。

例えば、CPLDを使うことで入力電圧3.3Vに対して1.8Vを出力したり、チップベンダー独自のインタフェースを業界標準プロトコルに変換したり、シリアル-パラレル・バス変換などを行ったりすることができる。また、複数のチップを接続するためのマルチポイント・バス・ブリッジといった機能もサポートされている。図4はLCDコントローラ・インタフェースの実装例である。

これまで2回(前編・後編)に分けて、最新CPLDの特徴やその用途について紹介した。民生電子機器はもとより、産業機器の開発においても、期間の短縮やコストダウン、消費電力の低減は一段と強く求められている。その解決法の1つとして、設計の柔軟性を提供するCPLDが広く採用されるようになった。パッケージも含めた製品群の拡充に加えて、開発ツール/開発キットやアプリケーション・ノートなどもかなり充実してきた。こうしたことがCPLD市場の拡大に結びついているのではないだろうか。

CPLDに関する設計情報を掲載したアルテラのWebページ「はじめてのCPLD設計」には、CPLDを使いこなすためのヒントがある。有効に活用されてみてはいかがだろうか。

関連情報

●低コスト・低消費電力CPLDによる5つの主要コントロール・パス・アプリケーションの実装

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.