第53回 デジタル信号処理(DSP)設計の基礎知識を学ぶ 〜産業機器向けモーター制御編〜:FPGA Insights

全世界の電力消費量は2007年の1万6500TWh(テラワット時)に対して、2030年には2万9000TWhと実に76%も増加する予測となっている。しかも、現在は電力の64%を産業用モーターが消費しているといわれている。こうした中で、駆動回路を工夫すればモーターのエネルギー消費を最大40%節約できる可能性がある。そこで注目を集めているのが、高速な制御ループを実現し、モーターの電力消費を低減しようという取り組みだ。モーターの効率改善は、エネルギーを節約する最大テーマの1つといえよう。

モデルベース設計によるモーター制御系のFPGA実装

昨今、世界各国でエネルギー規制が厳しさを増すなか、産業機器でもシステムの高機能化とともに低消費電力化が求められている。特に工業用電力の2/3を超える電力を消費するモーター駆動工業用機器では、その運用効率化が経費削減においても重要な要素となる。そのような産業機器向けモーターの制御回路を開発するに当たって、メーカーの課題もある。それは、さまざまな産業用イーサネット・プロトコルのサポートなど「パフォーマンスの改善」や、モデルベース設計フローの活用など「差異化とコスト削減の両立」、そして「機能安全の実装」などである。

本稿では、デジタル信号処理技術を用いた高速な制御ループの実現や、モーター制御用ICを開発するに当たっての課題を解決する手段の1つとして、アルテラが提供しているいくつかのソリューションを紹介する。

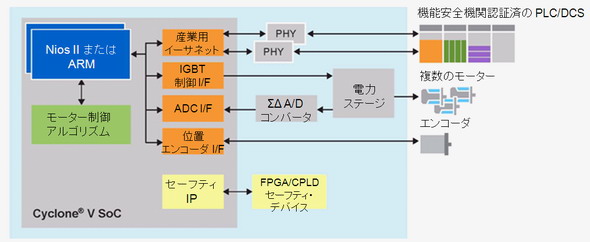

その1つがCyclone® V FPGAをベースとしたSoCによる統合ドライブ制御である。 図1に主要な回路ブロックを示す。組み込みコントローラとしてNios® IIプロセッサまたはARMコアが内蔵されている。モーター制御アルゴリズムは浮動小数点をサポートしたハードウェア・アクセラレータで実行する。FPGAには産業用イーサネットやIGBT制御インタフェースなどを実装することができる。さらに、機能安全機関であるTUVが認証した診断用IPがサポートされていることから、機能安全が求められるシステム開発において、アルテラのFPGAを利用すれば、関連する制御ブロックにおいて認証のための期間短縮が可能となる。一例だが、TUV認証済み機能安全・パッケージを使用すると、使用しない場合に比べて機能安全認証期間は18〜24カ月も短縮できるという。

モーター制御の世界ではマイコンやDSPが一般的だが、より高速な制御が要求される次世代のモーター駆動システムにおいては、複雑な演算アルゴリズムを高速に処理できる大きなコンピューティング能力やさまざまな要件に対応する性能スケーリング機能、システム統合と最適化への柔軟性を併せ持つプラットフォームが必要となる。高い演算性能や性能スケーリングと統合化の利点を有するFPGAが、モーターの高速制御に適している理由がここにある。

モーター制御用ICの設計に、アルテラのFPGAを使用することによって、高速な制御ループを実現することができ、モーター効率を向上させることができる。その上、「MATLAB®/Simulink®」によるモデルベース設計を行うことで、実機動作前の机上計算におけるアルゴリズムの完成度を飛躍的に高めることができる。しかも、コード生成ツールを使って、シミュレーション用モデルからHDL生成を行い、FPGA実装するためのHDL記述工程を削減すれば、さらなる工数削減にもつながる。このことによってモーターや電源回路、駆動系などの制御系設計を短時間で行うことが可能である。

なぜモデルベース設計が必要か

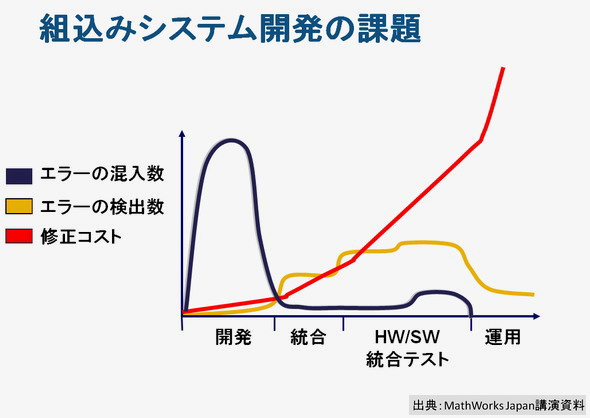

ここからは、一般的な組み込みシステムの開発者が直面している課題に触れた上で、モデルベース設計によるモーター制御系のFPGA実装について簡単に述べる。図2にエラーの混入数とエラーの検出数の相関関係を示す。この図から、開発の初期段階で多くのエラーが混入し、そのエラーを検出するにはある程度の時間を要することが分かる。エラーの検出が遅れるほど、修正コストも増えることになる。逆をいえば、設計の早い段階でエラーを発見することができれば、開発期間を短縮し、開発効率を高めることができる。開発コストの削減にもつながるわけだ。

しかし、実際のシステム開発において、システム開発者とFPGA開発者との間には、使っている開発ツールや担当者間の壁が存在する。この壁が開発の効率化を阻んでいるケースもある。この壁を取り除くためにはMATLAB/Simulinkの活用が有用である。例えばMATLAB/Simulinkの連携機能を使うことで、システム設計で使用したアルゴリズム資産を、ハードウェア実装に必要なHDLなどの別言語に容易に変換することができるからだ。

新しいシステムを開発する場合、さまざまな開発工程で多くの技術者が関わり、いくつかの開発ツールを使いこなす必要がある。このために設計者は各ツールの操作方法を新たに覚えたり、データの変換や再入力したりする作業が生じていた。

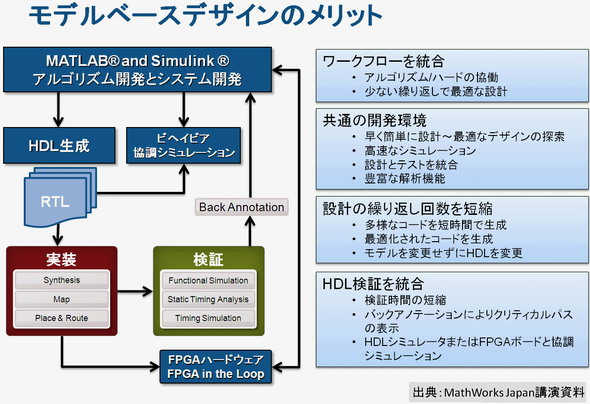

こうした中、アルゴリズム開発とシステム開発にMATLAB/Simulinkを用いれば、シミュレーション結果を可視化して直感的にみることができる。その上、開発ツールを連携することで、効率的な設計フローを実現することができる。設計フローとそのメリットを図3に示す。この効果として、混入するエラーを抑制し、かつエラーの検出を前倒しすることが可能となる。

小さい繰り返しループ

次に、モーター制御用IC開発におけるモデルベース設計の適用事例を簡単に紹介する。このユーザー事例ではモデルベース設計を導入する前は、開発品が正しく動作するかどうかを、FPGAプロトタイプとモーター実機を使って確認し、試行錯誤を繰り返していた。

モデルベース設計を導入した後は、動作確認がシミュレーションベースへと移行できた。このケースではSimulinkのオプションブロックライブラリであるフィジカルモデリングツール「SimPowerSystemsTM」ブロックを使った。このツールではシミュレーションによりモーターの動作確認が可能なため、実機でのやり直しを低減することができた。

モデルベース設計を導入したことで、期待値以上の効果も得られたという。それは、モーター(制御対象側)の特性ばらつきをシミュレーションで再現できたことだ。シミュレータを用いると、パラメータを変更しモーターの挙動を確認することが簡単にできる。変更に要する時間はわずか数十秒で済む。この速さは実機ベースではできなかった。開発工程における繰り返しループもSimulink上で行えるため従来に比べてはるかに小さくなった。

制御系設計におけるモデリング

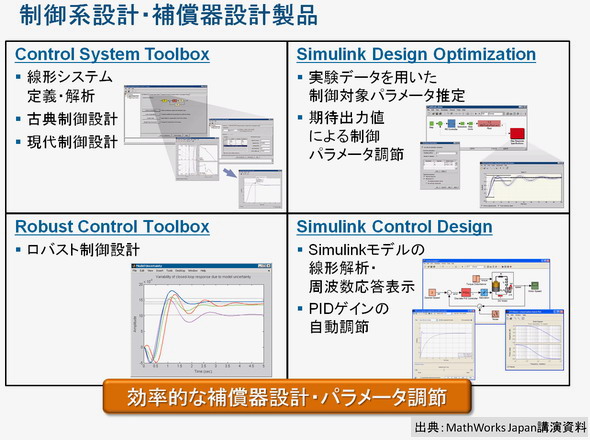

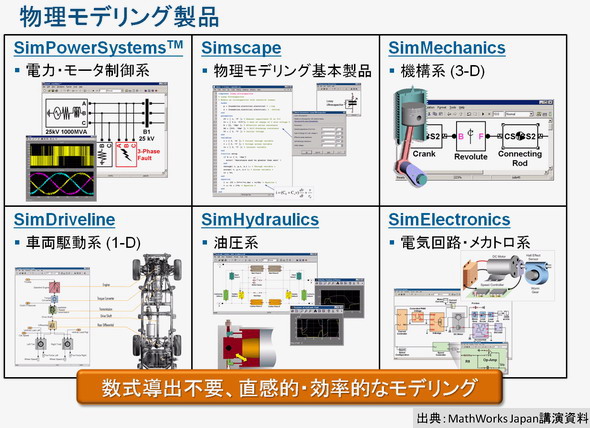

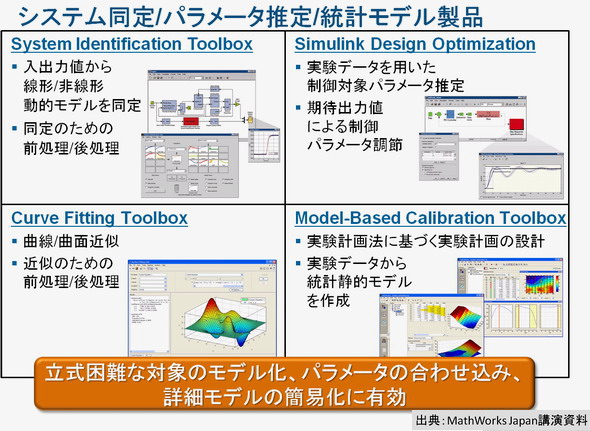

制御系設計におけるモデリングについても簡単に紹介する。制御系設計には「コントローラ設計」と「プラント設計」という2つの重要な要素がある。例えば、コントローラ側は「理論式や条件式」、「C/C++、Fortran、MATLAB言語」、「マップ特性」などを使い、プラント側は「理論式」、「物理特性」、「入出力特性」などを用いて、それぞれモデリングすることができる。これらを表現するため、MATLAB/Simulinkにはいくつもの手法が用意されている。コントローラ側のオプション製品として図4などが用意されている。また、プラント側のモデル化は2つのアプローチが用意されている。1つが物理モデリング製品(図5参照)で、もう1つはシステム同定/パラメータ推定/統計モデル製品である(図6参照)。

シミュレーションから実機テストへ

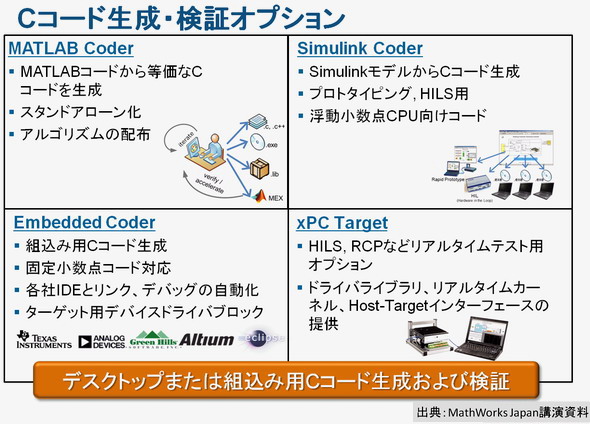

シミュレーションで得られた結果をベースに、実機でテストを行う場合のオプションも用意されている。Cコード生成・検証オプション(図7参照)である。さらに、今回は詳細な説明を行わないが、プラント(モーター)側はあるがコントローラ側がない場合に有用な「Rapid Control Prototyping(RCP)」や、プラント側はないがコントローラ側の動作をリアルタイムで検証したい場合に有用な「Hardware-in-the-Loop Simulation(HILS)」なども用意されている。近年は、プラント側をコンピュータで模擬するHILSにおいても、CPUに替わって制御周期の高速化のためにFPGAが使われ始めている。

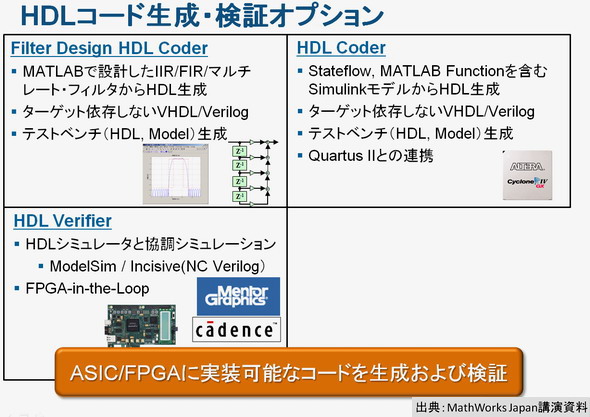

HDLコード生成/検証オプションとしては図8の通り、3つのツールが用意されている。特に、HDL Coderはアルテラの開発ソフトウェアQuartus® IIとの連携を図っている。

DSP Builderアドバンスト・ブロックセット

一方、アルテラでもMathWorks社のMATLAB/Simulinkで開発したDSPアルゴリズムを、アルテラ製の開発ソフトウェア「Quartus II」を使ってFPGAに実装するための合成ツール「DSP Builder」を用意している。最新のDSP Builderには、Simulinkブロックセット「アドバンスト・ブロックセット・ライブラリ」が追加されている。このライブラリには、浮動小数点のソフトウェア・ライブラリである「math.h」と同等のハードウェアライブラリが含まれている。設計者が設定したシステムレベル・デザイン制約に適合するように、パイプライン化されたステージおよびレジスタを自動的に追加する機能などを備えているのが特徴だ。この機能によって、Cyclone® IV / III FPGAの場合150M〜250MHzのクロック・レートでタイミング収束が可能となる。

また、Cyclone V FPGA では、各DSPブロックでコンフィグレーション可能な可変精度DSPブロックがサポートされたことにより、ハードウェアリソースをより有効に活用し、大規模で高精度なDSPを実現可能とした。

本稿では、産業機器向けモーター制御とMATLAB/Simulinkを活用したFPGA開発のメリットについて述べてきた。ライブラリを活用することによるシミュレーション工数の削減、汎用HDL生成とテストベンチ生成によるコーティング時間/検証時間の削減などが期待でき、最終的に開発期間を短縮できることが最大のメリットである。

なおMathWorks社では、購入を検討しているユーザーに対して、MATLAB/Simulinkを購入前に30日間無料で使える評価版を用意している。詳細はこちら。

関連情報

統合FPGAデザイン・フローによるモーター制御デザインの最適化

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2014年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.