アナログ回路のトランジスタがバイポーラからMOSへと移行した理由は、デジタル回路と基本的には同じです。高密度化が容易であることと、消費電力が低いことです。ただし、デジタル回路に比べると移行の時期は遅くなりました。MOSトランジスタはアナログ性能ではバイポーラ・トランジスタに劣っていたからです。

しかしMOSトランジスタの高密度化(微細化)が指数関数的に進んだ結果、バイポーラとMOSではシリコンダイ面積(面積が大きくなると製造コストが上昇します)の差が無視できなくなるほど、広がってしまいました。MOSアナログの方が、ずっと小さなシリコンダイになるのです。

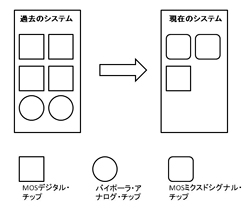

そしてきわめて重要な要因に、アナログ回路とデジタル回路を混載した半導体チップの登場と普及があります。MOSデジタル回路の高密度化によってシリコンダイにアナログ回路を混載する製品が増加してきたのです。アナログ回路だけを載せた半導体チップの割合は減少していきました。現在では、アナログ回路のほとんどはデジタル回路と混載されるようになっています。

バイポーラ・トランジスタの製造プロセスとMOSトランジスタの製造プロセスは根本的に異なります。このため、両者を同じシリコン半導体チップに混載したのでは、製造コストが跳ね上がってしまいます。製造コストを低く抑えることは半導体チップにおいては至上命題ですので、アナログ回路もデジタル回路と同様に、MOSトランジスタで構成することになります。MOSトランジスタのアナログ性能が少々劣っていても、半導体チップ全体で要求仕様を満足すれば、製品としては成立します。

また前回(第11回)に述べたように、雑音や周波数特性、利得などではバイポーラに比べるとMOSトランジスタは劣っていたのですが、MOSトランジスタの微細化がさらに進んだ結果、いくつかの特性ではシリコン・バイポーラと同等、あるいはシリコン・バイポーラをしのぐようになってきました。例えば動作周波数(トランジション周波数または最大動作周波数)や伝達コンダクタンスといった特性です。おおよそ0.1μm(100nm)の世代あたりからは、シリコンMOSがシリコン・バイポーラ(ここではシリコン・ゲルマニウムは除いています)を超える性能を発揮するようになってきました。

こういった時代の流れから、0.1μm(100nm)前後、あるいはそれよりも微細な加工技術を駆使する半導体チップでは、アナログ回路だけを内蔵した製品はほとんどみられなくなりました。アナログ回路とデジタル回路の混載チップ、いわゆる「ミクスドシグナル」と呼ばれる製品がごく普通になっています。なおミクスドシグナルに対し、アナログ回路だけを搭載したチップを「純アナログ」あるいは「ピュア・アナログ(pure analog)」と呼ぶことがあります。

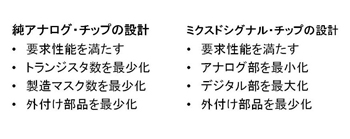

ミクスドシグナルの回路設計における基本思想は、アナログ部分を極力少なくすることです。なぜかというと、アナログ部分はデジタル部分に比べると回路の密度が大幅に低いからです。例えば、回路素子全体の5%以下がアナログ部分だとしても、シリコン半導体チップ全体の面積に占めるアナログ部分の割合は3分の1近くになったりすることがあります。これはMOSトランジスタそのものは小さくできるものの、受動素子であるコンデンサやインダクタなどは小さくしづらく、このためにある程度のシリコン面積を必要とする、といったことが大きな理由です。

また、アナログ回路を構成するコンデンサとインダクタの定数によっては、シリコン半導体に内蔵できず、半導体パッケージのピンに別部品として単体のコンデンサまたはインダクタを外付けすることもあります。こうなると半導体ユーザーは半導体チップ以外に受動部品を購入しなければならず、購入の手間が増えるとともに、プリント基板への実装面積が増大し、プリント基板の製造コストが増えてしまいます。

そこでミクスドシグナルの回路設計では、デジタル回路の規模が少々増えても構わないから、アナログ回路を減らすとともに、外付け部品を減らすことが求められます。純アナログ回路の設計では、アナログ回路の工夫によって要求性能を満足させながらシリコン面積を節約する(トランジスタ数を最少化する)ことが求められていました。純アナログからミクスドシグナルへの変化は、半導体チップの設計思想も変化させたことが分かります。

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.