第10回 トランシーバを内蔵した低コストFPGAの活用法(後編):FPGA Insights

主なFPGAメーカーは、新たな成長領域に向けた製品の拡充に取り組んでいる。その背景と主要製品の特徴などについては前編で述べた。後編では、民生電子機器や産業機器、放送機器などの製品開発にかかわるコスト低減や新技術への移行にも柔軟に対応できるFPGAについて、アルテラの最新製品「Cyclone IV GX」シリーズを取り上げ、内蔵された高速シリアルインターフェースを活用した設計事例などを紹介する。

フルHD解像度の画像を4対のI/Oで対応

・応用事例その1:HDTV

デジタルテレビ市場は拡大を続けている。特にLCDテレビの出荷台数は年平均成長率が22%と高い伸びとなっている。大量生産されるデジタルテレビにおいても、高速な動画処理や広帯域幅が求められるチップ間通信などの用途にFPGAを用いるケースが増えてきた。例えば、タイミングコントローラ(TCOM)やディザリングなどのビデオ処理、フレームレート変換、LEDバックライトユニットの局所輝度制御、「V-by-One」や「DisplayPort」など次世代プロトコルによるディスプレイインターフェース、といった機能を実現するためにFPGAが適用されている。さらに、次世代デジタルテレビでは、3D表示や高フレームレート(120MHz以上)などの最新技術が採用される見通しで、機器設計者はこのような技術進歩への迅速な対応が求められている。

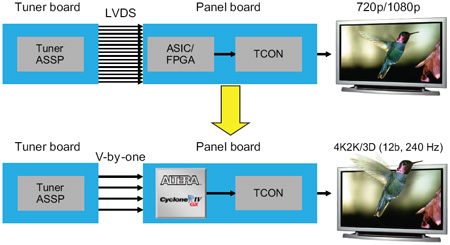

高精細デジタルテレビ(HDTV)での一例を挙げると、HDTV(720p)に搭載されているチューナ(あるいはビデオ信号処理)用プリント基板と液晶パネル用プリント基板を接続するためのインターフェースとして、現在は16対のLVDSが用いられている(図1)。しかし、3D表示機能を含め、次世代のフルHDTVと呼ばれる製品では、「新しいビデオ規格」、「4k×2k(3840×2160)の解像度」、「240Hzの垂直走査周波数」といった仕様が明らかとなっている。これらの仕様に対応しようとすれば、チューナ(あるいはビデオ信号処理)基板と液晶パネル基板間を従来と同様にLVDSで接続した場合、最大36対のLVDSが必要となる。

しかし、I/O数が増加すればプリント基板のサイズが大きくなったり、プリント基板の層数が増加したり、消費電力の増大につながったりすることになる。こうした課題を解決する1つの方法として、「V-by-One」と呼ばれる新しいシリアルプロトコル規格を採用する動きがある。このV-by-Oneは、4対で用いることにより、フルHDTVで要求される解像度4K×2Kをサポートするための十分な帯域幅を備えている。つまり、LVDSであれば36対のケーブルを必要としたが、V-by-Oneを用いると4対のケーブルで済むことになり、システムコストの削減策としてはとても有効となる。その上、V-by-Oneプロトコルを用いることで、LVDSケーブル/コネクタを使った場合に比べて、シグナルインティグリティ(SI)も改善することができる。

また、LEDチップを用いたバックライトシステムは、液晶テレビの画像の鮮明度をさらに向上させる技術として注目されている。現状では、バックライトに使われるLEDの制御に関する規格は業界として策定されておらず、テレビメーカーごとに独自の制御アルゴリズムを採用している。それは画面サイズによっても異なるため、今後も制御アルゴリズムの最適化は進み、順次変更される可能性は高い。このように仕様変更が予想されるような場合の回路設計にはFPGAが適している。Cyclone IV GXは、ディスプレイインターフェースのボトルネックを解消するためのトランシーバを実装でき、既存のビデオプロセッサと連動して、LEDバックライトのビデオコプロセッシングの役割を担うことができる。

PCIeのハードIPブロックを搭載

・応用事例その2:ASIC/ASSP

2つの別々なICチップ間を接続する場合、各チップが対応している電圧レベルや規格、プロトコルがまったく異なる場合には、チップ間をブリッジ(インターフェースを変換)する必要がある。例えば、低価格のASICとASSPを組み合わせて使用する際に、PCIeバスがサポートされていない場合には、新たにその機能を付加したASICを設計する必要がある。このような開発環境で、PCIeバスをサポートしているCyclone IV GXを用いると、新たにASICを設計する必要がなく、そのための費用削減や開発時間が不要となる。

特に、Cyclone IV GXにはPCIeバス用のハードIPブロックが用意されている。このため、PCIeバスインターフェースをFPGAに実装する場合でも 内部のロジックを使う必要がなく、ロジック規模が比較的小さく安価なFPGAを用いることができる。しかも、このハードIPブロックはPCIe Gen1に準拠した性能を備え、×1、×2、×4レーンをサポートしている(図2)。

・応用事例その3:エンベデッドコントローラ

マイクロコントローラをベースとした組み込み機器においては、一般的にモデルチェンジを繰り返すごとに部品コストの削減に対する要求は厳しいものとなっている。この課題を解決するための新たなアプローチの1つは、FPGAをベースにチップを再設計することでBOMコストを削減することである。最新のFPGAは、微細加工技術を適用することで集積度も高まり、低価格で多数のロジック回路を実装することができるようになった。例えば、Cyclone IV GXシリーズは、32ビットソフトIPプロセッサ「Nios II」をシステム制御に用い、内蔵した18×18ビット乗算器を使って、大量のデジタル信号処理またはアルゴリズム処理を並列で実行できる。さらに、外部トランシーバやSERDES、PHY ASSP機能までをもチップに取り込むことができるようになっている(図3)。

・応用事例その4:ビデオサーバーとビデオキャプチャ

ノンリニア編集を行うためにビデオサーバーとビデオI/Oカードの間では、SDI-PCIeブリッジが使用される。基本となるビルディングブロックを組み合わせて、PCIeバスを使用したビデオストリーミング機能を実装し、SDIケーブルイコライザとドライバをフロントエンドインターフェースとして使用する。ビデオストリーミング/プロセッシング用のコアは中央ブロックに組み込まれる。Cyclone IV GXを使用すればこれらの回路ブロックに加え、PCIeバスインターフェースもハードIPブロックで組み込むことができる。SDI-PCIeブリッジの回路ブロックの一例を図4に示す。

ビデオサーバーとビデオキャプチャI/Oカードは、同じ基本ハードウエアアーキテクチャのフロントエンドを共有している。機器メーカーにより、取り込み機能と送出機能を1つのカードに実装されることもあれば、個別のカードに実装されていることもある。サーバーの中には、ビデオプロセッシングブロック内でH.264またはMPEG2-HDを使用して編集前のビデオ信号をエンコードまたはデコードするオプションを提供しているものもある。

PCIeブロックは、変換されたSDI信号をワークステーションに供給するためのビデオストリーミング機能をもつ。しかし、このブロックが複数の3G-SDIストリームを同時に実行するときに、しばしばボトルネックとなる場合がある。4レーンのPCIeカードを介した3G-SDI全二重ビデオストリーミングのデータレートは3.375 Gbpsに達するため、PCIeブロックは高効率であると同時に高品質なサービスを提供できなくてはならない。

Cyclone IV GXのPCIeハードIPブロックは、x1、x2、またはx4レーンのオプションとエンドポイント/ルートポート機能を備えたPCIe Gen1に準拠している。この機能は同等の低コストFPGAではサポートされておらず、現状ではCyclone IV GXだけが備えている機能である。

ASICやASSPの設計に慣れ親しんだ技術者にとって、FPGAはこれまで敷居の高い製品だったかもしれない。しかし、開発期間の短縮やシステム全体のコスト低減、新しいインターフェース技術への迅速な対応などを迫られている機器設計者にとって、民生電子機器や産業機器、ワイヤレス機器などの用途でも、低コスト/低消費電力のFPGAを回路設計に活用してみる価値は十分にありそうだ。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●業界最小コスト、最小消費電力FPGAによるトータル・システム・コストの削減

●Supporting Digital Television Trends with Next-Generation FPGAs[英文](和文は5月上旬リリース予定)

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.