第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜:FPGA Insights

本連載「DDR2 の実装からデバッグ手法」では、「ボードを使った回路設計」の一例として、FPGAを使った「DDR2 SDRAMインタフェース回路の設計」をテーマに取り上げて解説している。前回のステップ1では「トポロジーの検討」および「伝送シミュレーション」について述べた。今回のステップ2では、IPコアを使ったDDR2 SDRAMインタフェース回路の設計と、そのシミュレーションについてわかりやすく解説する。最新のFPGA設計ツールとIPコアを活用することで、FPGAの設計が比較的容易であることを実感していただきたい。

FPGAの設計開発フローの中で、「これさえ知っていればFPGAの設計ができる」という4つの基本ステップを、これまで4回にわたって連載し、一歩ずつ解説してきた。前回からは、FPGAなどのICチップが実装されたプリント基板を使った、より実践的な「ボードを使った回路設計」について、DDR2 SDRAMインタフェース回路の設計における「トポロジー検証の段階からデバッグ手法まで」を2回に分けて紹介している。

DDR2 FPGA デザイン設計

今回のステップ2では、FPGA 内部のデザイン設計方法について紹介する。ボードを使った回路設計を行う場合、回路図設計に着手する前にFPGA 内部のデザインもある程度は終わらせておく必要がある。それはピン配置などを事前に決めておかなくてはならないためだ。

一般的に、『DDR2 SDRAMコントローラの設計』と聞いただけで、設計者は「手間がかかる」、「IP を使用した場合にコストがかかる」と思い込みがちだが、アルテラ製FPGAおよび「HardCopy ASIC」は、チップ内部にDDR2 SDRAMインタフェース回路を集積するための「PHY IPコア」および「コントローラ・ソリューション」を提供している。これらを活用すれば、思ったよりも簡単に DDR2 SDRAMインタフェース回路をFPGAに実装することができる。

そこで今回は、アルテラ社が用意しているIPコア「DDR2 SDRAM High Performance Controller」 を活用して、DDR2 SDRAMインタフェース回路をFPGAで実現するための方法を紹介する。操作方法は非常にシンプルである。アルテラ社製の開発ソフトウエア「Quartus II ソフトウエア サブスクリプション・エディション」を購入すると、無償で提供されるDDR2 SDRAM High Performance Controllerを使えば、基本的に以下に示す 3つのステップを実行するだけで、DDR2 SDRAMインタフェース回路を実現することができる。

3ステップでDDR2 を実現

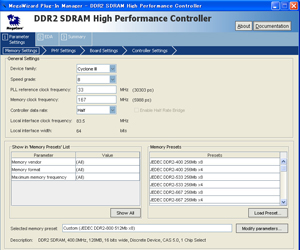

その1:Quartus IIの IP ToolBench に必要なパラメータを入力

Quartus II の「 IP ToolBench 」に、使用するFPGAのファミリ名やデータレート、メモリ仕様など必要となるパラメータを入力するだけで、あとは開発ツールが最適なデザインを自動生成してくれる。同時にシミュレーション用のテストベンチを生成する機能も備えている。

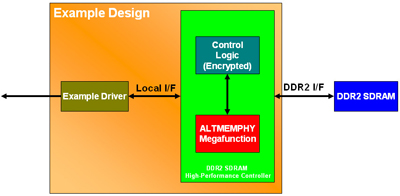

具体的には、IP ToolBench に必要事項を入力し、その入力作業が終了すると、DDR2 SDRAM コントローラのデザインが自動的に生成される(図2)。その上、サンプルデザインを含んだラッパファイルも自動生成されている。ラッパファイル<コントローラ名_example_top> は、ローカルのサンプルデザイン“example driver”、“DDR SDRAM High-Performance Controller” をインスタンスしているデザインとなる。また、自動生成されたサンプルのラッパファイルを使用すると、「 Read Data 」と「 Write Data 」の適合性を確認し、その結果を “pnf (pass not fail)” ポートでモニタリングすることができる。これにより、ユーザーデザインを設計する前に、DDR2 SDRAMインタフェースの Read/Write 試験が行え、デバッグ時の原因の切り分けにも非常に役に立つ。

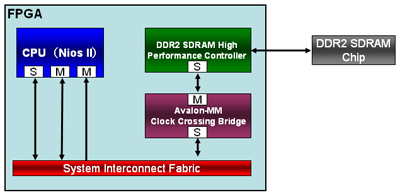

図2の「Example Design 」は、IP コア(DDR2 SDRAM High Performance Controller) を検証するデザインであり、実際には CPU と接続して使用されることが多い。アルテラ社のFPGAでは図3の通りFPGA 内に CPU(Nios II プロセッサ) を組み込むことができる。このことにより、DDR2 SDRAM インタフェースを備えたSoCの開発が可能となる。

また、CPU(Nios II プロセッサ)と DDR2 SDRAM High Performance Controller との接続作業も「SOPC Builder」上で簡単に行うことができる。

その2:ピン配置

DDR2 SDRAMインタフェース回路を FPGA で実現する場合、I/O 制約が必要となる。ところが、IP ToolBench を使用すると、I/O 制約を行ってくれる実行ファイルが作業終了時に自動生成される。このため、設計者は生成されたその実行ファイルを実行して、ピン配置を行うだけで済む。

その3:コンパイルの実行

コンパイルを実行する前には各種制約を設定する必要があることは、前回連載した「FPGAの設計開発フローのステップ2」でも述べた。制約を設定する項目はタイミング制約であったり、上述したI/O 制約であったりと、なにかと工数がかかるイメージがある。しかし、DDR2 SDRAM High Performance Controller を使用すれば、コア生成と同時にスクリプトファイルとタイミング制約で使用する「 .sdc 」ファイルが自動生成される。各スクリプトファイルを実行するだけで、I/O 制約と同じように、 DDR2 SDRAM High Performance Controller に関する制約の設定が行われる。また、タイミングの詳細な解析・制約は「 TimeQuest 」を使用することにより GUI 上で行うことができる。

FPGAの設計開発フローのステップ3で述べたように、制約設定が終了した後に、コンパイルの作業を行う。画面上のアイコンをクリックするだけでコンパイルの作業が始まり、論理合成、配置配線、プログラミングファイルの生成といった一連の作業をQuartus II が自動的に実行する。

以上でデザイン設計の作業は終了となる。あとは、FPGA にプログラミングするだけである。

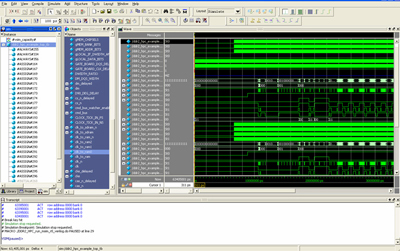

シミュレーション

DDR2 SDRAM High Performance Controller を使用すると、前述した通り、テストベンチが同時に自動作成される。その分、設計者の手間を省けることになり、大幅な工数削減となる。また、シミュレーション用の実行ファイルも生成されるので、容易にシミュレーションを実行することができる。アルテラ社では Mentor Graphics 社製の言語シミュレータである、「ModelSim-Altera Starter Edtion 」を 無償提供しているので、今回はこのシミュレータを使用した。

このように、アルテラ社の FPGA と開発ソフトウエアを使えば、最初にパラメータの設定を行うだけで、そのあとは必要なファイルの生成を開発ソフトウエアが自動的に行ってくれる。このため、高速メモリインタフェース回路を設計した経験や実績が十分でない技術者でも、DDR2 SDRAMコントローラの設計が比較的簡単に行える。また、ASIC とは違い、プリント基板に実装した後もFPGA の回路データを書き換えることが可能である。このため、たとえ設計した回路に問題が発生した場合でも、FPGA の設定を変更することで、不具合が改善されるケースが多く見受けられる。

次回の「DDR2 の実装からデバッグ手法:ステップ3」では「FPGAのデバッグ手法」として、Quartus II が備えるオンチップ・デバッグ機能「SignalTap II Logic Analyzer」の操作方法などについてわかりやすく解説する。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●POS-PHY Level 4 MegaCore ファンクション用シミュレーション・モデルのアップデート

●SOPC BuilderによるDDR/DDR 2 SDRAMの使用

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.